# GOVT. POLYTECHNIC BARGARH

# **LECTURE NOTE**

**POWER ELECTRONICS & PLC**

SEMESTER-5<sup>TH</sup>

EE/EEE ENGINEERING

PREPARED BY

NIRANJAN NAYAK

Lect. (S-II) IN AE&I Engineering

# **Chapter-1: Power Semiconductor devices**

## 1.1 Power Diode

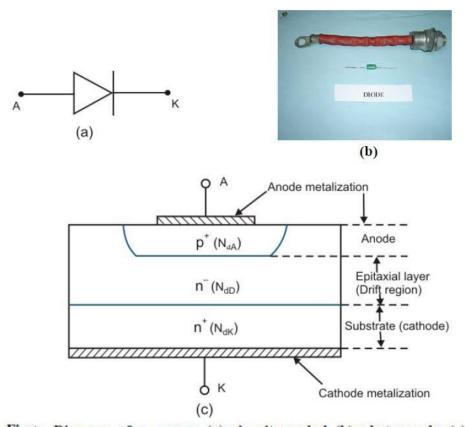

# 1.1.1 Explain the operation, construction & application of Power Diode

Power Diodes of largest power rating are required to conduct several kilo amps of current in the forward direction with very little power loss while blocking several kilo volts in the reverse direction. Large blocking voltage requires wide depletion layer in order to restrict the maximum electric field strength below the -impact ionization level. Space charge density in the depletion layer should also be low in order to yield a wide depletion layer for a given maximum Electric fields strength. These two requirements will be satisfied in a lightly doped p-n junction diode of sufficient width to accommodate the required depletion layer. Such a construction, however, will result in a device with high resistively in the forward direction. Consequently, the power loss at the required rated current will be unacceptably high. On the other hand if forward resistance (and hence power loss) is reduced by increasing the doping level, reverse break down voltage will reduce. This apparent contradiction in the requirements of a power diode is resolved by introducing a lightly doped -drift layer of required thickness between two heavily doped p and n layers as shown in Fig 1 (c). Fig 1 (a) and (b) shows the circuit symbol and the photograph of a typical power diode respectively.

Fig.1: Diagram of a power; (a) circuit symbol (b) photograph; (c) schematic cross

To arrive at the structure shown in Fig 1 (c) a lightly doped **n** epitaxial layer of specified width (depending on the required break down voltage) and donor atom density (N) is grown on a heavily doped **n**+ substrate (NdK donor atoms. Cm-3) which acts as the cathode. Finally the **p-n** junction is formed by defusing a heavily doped (NaA acceptor atoms.Cm-3) **p**+ region into the epitaxial layer. This **p** type region acts as the anode.

The different applications of Power Diode are in SMPs, Snubber, Chopper and freewheeling diode etc.

# 1.1.2 Explain V-I characteristics curve of Power Diode

Power Diodes take finite time to make transition from reverse bias to forward bias condition (switch ON) and vice versa (switch OFF). Behavior of the diode current and voltage during these switching periods are important due to the following reasons.

- i) Severe over voltage / over current may be caused by a diode switching at different points in the circuit using the diode.

- ii) Voltage and current exist simultaneously during switching operation of a diode. Therefore, every switching of the diode is associated with some energy loss. At high switching frequency this may contribute significantly to the overall power loss in the diode.

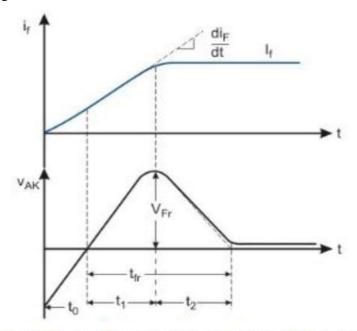

**Observed Turn ON behavior of a power Diode:** Diodes are often used in circuits with di/dt limiting inductors. The rate of rise of the forward current through the diode during Turn ON has significant effect on the forward voltage drop characteristics. A typical turn on transient is shown in Fig. 2

Fig. 2: Forward current and voltage waveforms of a power diode during Turn On operation.

It is observed that the forward diode voltage during turn ON may transiently reach a significantly higher value Vfr compared to the steady slate voltage drop at the steady current IF. Vfr (called forward recovery voltage) is given as a function of the forward di/dt in the manufacturer's data sheet. Typical values lie within the range of 10-30V. Forward recovery time (tfr) is typically within 10 us.

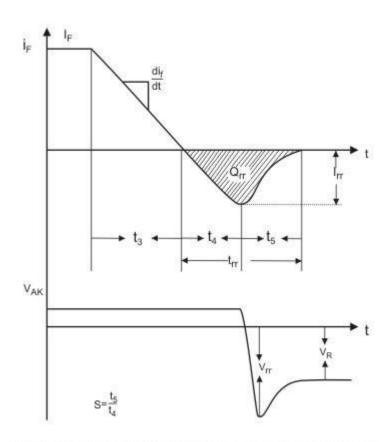

**Observed Turn OFF behavior of a Power Diode:** Figure 3 shows a typical turn off behavior of a power diode assuming controlled rate of decrease of the forward current.

Fig. 3: Reverse Recovery characteristics of a power diode

Salient features of this characteristic are:

The diode current does not stop at zero, instead it grows in the negative direction to Irr called -peak reverse recovery current which can be comparable to IF. In many power electronic circuits (e.g. choppers, inverters) this reverse current flows through the main power switch in addition to the load current. Therefore, this reverse recovery current has to be accounted for while selecting the main switch.

Voltage drop across the diode does not change appreciably from its steady state value till the diode current reaches reverse recovery level. In many power electric circuits (choppers, inverters) this may create an effective short circuit across the supply, current being limited only by the stray wiring inductance. Also in high frequency switching circuits (e.g, SMPS) if the time period t4 is comparable to switching cycle qualitative modification to the circuit behavior is possible.

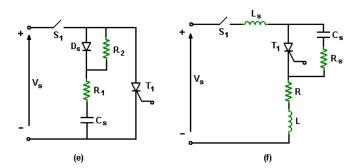

Towards the end of the reverse recovery period if the reverse current falls too sharply, (low value of S), stray circuit inductance may cause dangerous over voltage (Vrr) across the device. It may be required to protect the diode using an RC snubber.

During the period t5 large current and voltage exist simultaneously in the device. At high switching frequency this may result in considerable increase in the total power loss.

## **1.2 SCR**

# 1.2.1 Layer diagram of SCR and operation & construction of SCR.

Thyristors (also known as the Silicon Controlled Rectifiers or SCRs)

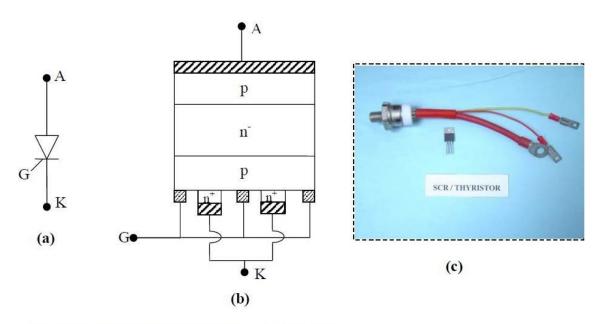

Fig. 4.1: Constructional features of a thysistor

(a) Circuit Symbol, (b) Schematic Construction, (c) Photograph

As shown in Fig 4.1 (b) the primary crystal is of lightly doped  $\mathbf{n}$  type on either side of which two  $\mathbf{p}$  type layers with doping levels higher by two orders of magnitude are grown. As in the case of power diodes and transistors, depletion layer spreads mainly into the lightly doped  $\mathbf{n}$  region. The thickness of this layer is therefore determined by the required blocking voltage of the device. However, due to conductivity modulation by carriers from the heavily doped  $\mathbf{p}$  regions on both side during ON condition the -ON state voltage drop is less. The outer  $\mathbf{n}$  layers are formed with doping levels higher then both the  $\mathbf{p}$  type layers. The top  $\mathbf{p}$  layer acls as the -Anode terminal while the bottom  $\mathbf{n}$  layers acts as the -Cathode The -Gate terminal connections are made to the bottom  $\mathbf{p}$  layer.

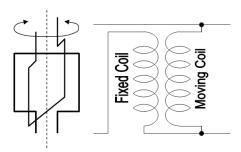

For better switching performance it is required to maximize the peripheral contact area of the gate and the cathode regions. Therefore, the cathode regions are finely distributed between gate contacts of the **p** type layer. An -Involute structure for both the gate and the cathode regions is a preferred design structure.

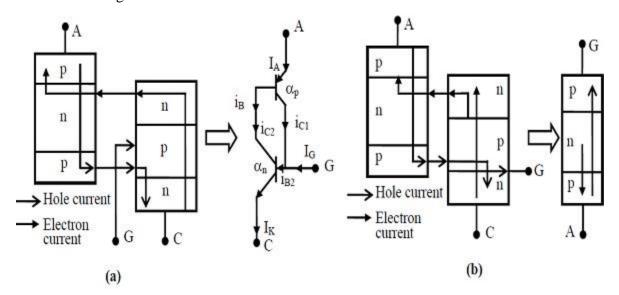

## 1.2.2 Explain the two transistor analogy of SCR

# Basic operating principle of a thyristor

The underlying operating principle of a thyristor is best understood in terms of the -two transistor analogy || as explained below.

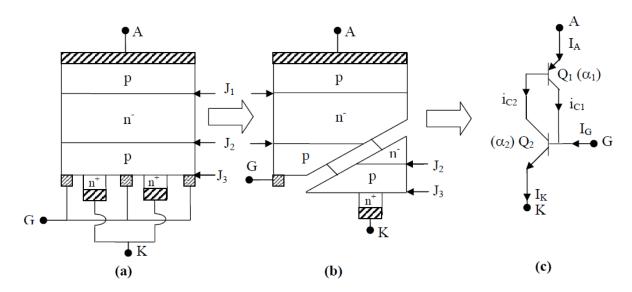

Fig. 4.2: Two transistor analogy of a thyristor construction.

- (a) Schematic Construction, (b) Schematic division in component transistor

- (c) Equivalent circuit in terms of two transistors.

- a) Schematic construction,

- b) Schematic division in component transistor

- c) Equivalent circuit in terms of two transistors.

Let us consider the behavior of this p n p n device with forward voltage applied, i.e anode positive with respect to the cathode and the gate terminal open. With this voltage polarity J & J are forward biased while J reverse biased.

Under this condition.

$$ic_1 = \infty_1 I_A + I_{co1}$$

(4.1)

$$ic_2 = \infty_2 I_K + I_{co2} \qquad (4.2)$$

Where  $a_1 \& a_2$  are current gains of  $Q_1 \& Q_2$  respectively while  $I_{co1} \& I_{co2}$  are reverse saturation currents of the CB junctions of  $Q_1 \& Q_2$  respectively.

Now from Fig 4.2 (c).

$$i_{c1} + i_{c2} = I_A$$

(4.3)

&  $I_A = I_K$  (4.4) (:  $I_G = 0$ )

Combining Eq 4.1 & 4.4

$$I_{A} = \frac{I_{co1} + I_{co2}}{1 - (\alpha_{1} + \alpha_{2})} = \frac{I_{co}}{1 - (\alpha_{1} + \alpha_{2})} \quad (4.5)$$

Where  $I_{co} \triangleq I_{co1} + I_{co2}$  is the total reverse leakage current of  $J_2$

Now as long as  $V_{AK}$  is small  $I_{co}$  is very low and both  $a_1$  &  $a_2$  are much lower than unity. Therefore, total anode current  $I_A$  is only slightly greater than  $I_c$ . However, as  $V_{AK}$  is increased up to the avalanche break down voltage of  $J_{2,co}$  starts increasing rapidly due to avalanche multiplication process. As  $I_{co}$  increases both  $a_1$  &  $a_2$  increase and  $a_1 + a_2$  approaches unity. Under this condition large anode current starts flowing, restricted only by the external load resistance. However, voltage drop in the external resistance causes a collapse of voltage across the thyristor. The CB junctions of both  $Q_1$  &  $Q_2$  become forward biased and the total voltage drop across the device settles down to approximately equivalent to a diode drop. The thyristor is said to be in —ONII state.

Just after turn ON if  $I_a$  is larger than a specified current called the Latching Current  $I_L$ ,  $a_1$  and  $a_2$  remain high enough to keep the thyristor in ON state. The only way the thyristor can be turned OFF is by bringing  $I_A$  below a specified current called the holding current ( $I_H$ ) where upon  $a_1$  &  $a_2$  starts reducing. The thyristor can regain forward blocking capacity once excess stored charge at  $I_2$  is removed by application of a reverse voltage across A & K (ie, K positive with respect A).

It is possible to turn ON a thyristor by application of a positive gate current (flowing from gate to cathode) without increasing the forward voltage across the device up to the forward break-over level. With a positive gate current equation 4.4 can be written as

$$I_{K} = I_{A} + I_{G} \qquad (4.6)$$

Combining with Eqns. 4.1 to 4.3

$$I_{A} = \frac{\alpha_{2} I_{G} + I_{co}}{1 - (\alpha_{1} + \alpha_{2})} \qquad (4.7)$$

Obviously with sufficiently large I the thyristor can be turned on for any value of I  $_{G}$  (and hence  $V_{AK}$ ). This is called gate assisted turn on of a Thyristor. This is the usual method by which a thyristor is turned ON.

When a reverse voltage is applied across a thyristor (i.e, cathode positive with respect to anose.) junctions  $J_1$  and  $J_3$  are reverse biased while  $J_2$  is forward biased. Of these, the junction  $J_3$  has a very low reverse break down voltage since both the  $\mathbf{n}^+$  and  $\mathbf{p}$  regions on either side of this junction are heavily doped. Therefore, the applied reverse voltage is almost entirely supported by junction  $J_1$ . The maximum value of the reverse voltage is restricted by

- a) The maximum field strength at junction J (avalanche break down)

- b) Punch through of the lightly doped n layer.

Since the **p** layers on either side of the **n** region have almost equal doping levels the avalanche break down voltage of  $J_1 & J_2$  are almost same. Therefore, the forward and the reverse break down voltage of a thyristor are almost equal. Up to the break down voltage of  $J_1$  the reverse current of the thyristor remains practically constant and increases sharply after this voltage. Thus, the reverse characteristics of a thyristor is similar to that of a single diode.

If a positive gate current is applied during reverse bias condition, the junction  $J_3$  becomes forward biased. In fact, the transistors  $Q_1 \& Q_2$  now work in the reverse direction with the roles of their respective emitters and collectors interchanged. However, the reverse  $a_1 \& a_2$  being significantly smaller than their forward counterparts latching of the thyristor does not occur. However, reverse leakage current of the thyristor increases considerably increasing the OFF state power loss of the device.

If a forward voltage is suddenly applied across a reverse biased thyristor, there will be considerable redistribution of charges across all three junctions. The resulting current can become large enough to satisfy the condition  $\mathbf{a}_1 + \mathbf{a}_2 = 1$  and consequently turn on the thyristor. This is called dvdt turn on of a thyristor and should be avoided.

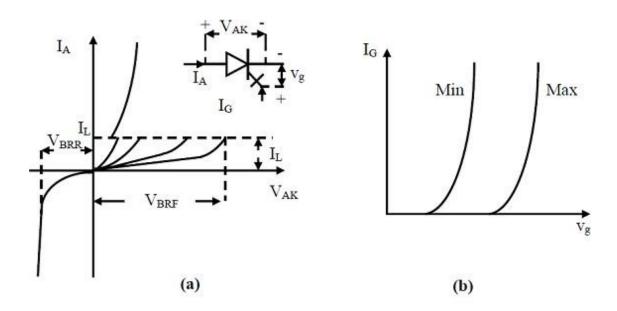

## 1.2.3 Static V-I characteristics & Dynamic characteristics of SCR.

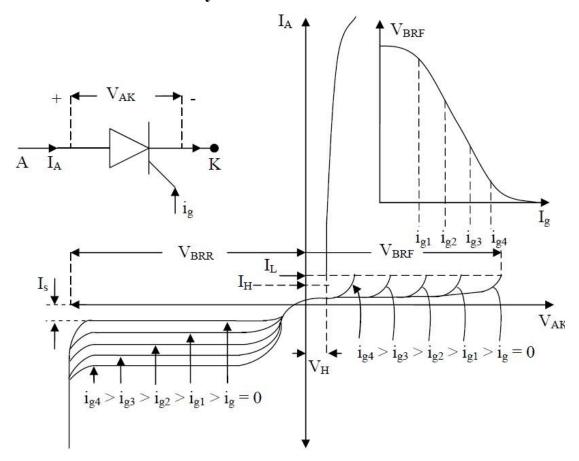

Fig. 4.3: Static output characteristics of a Thyristor

The circuit symbol in the left hand side inset defines the polarity conventions of the variables used in this figure.

With ig = 0,  $V_{AK}$  has to increase up to forward break over voltage  $V_{BRF}$  before significant anode current starts flowing. However, at  $V_{BRF}$  forward break over takes place and the voltage across the thyristor drops to  $V_{H}$  (holding voltage). Beyond this point voltage across the thyristor  $(V_{AK})$  remains almost constant at  $V_{H}$  (1-1.5v) while the anode current is determined by the external load.

The magnitude of gate current has a very strong effect on the value of the break over voltage as shown in the figure. The right hand side figure in the inset shows a typical plot of the forward break over voltage  $(V_{\overline{BRF}})$  as a function of the gate current  $(I_g)$

After -Turn ON the thyristor is no more affected by the gate current. Hence, any current pulse (of required magnitude) which is longer than the minimum needed for -Turn ON is sufficient to effect control. The minimum gate pulse width is decided by the external

circuit and should be long enough to allow the anode current to rise above the latching current  $(I_{L})$  level.

The left hand side of Fig 4.3 shows the reverse i-v characteristics of the thyristor. Once the thyristor is ON the only way to turn it OFF is by bringing the thyristor current below holding current (I<sub>H</sub>). The gate terminal has no control over the turn OFF process. In ac circuits with resistive load this happens automatically during negative zero crossing of the supply voltage. This is called -natural commutation or -line commutation. However, in dc circuits some arrangement has to be made to ensure this condition. This process is called -forced commutation.

During reverse blocking if  $i_g = 0$  then only reverse saturation current  $(I_s)$  flows until the reverse voltage reaches reverse break down voltage  $(V_{BRR})$ . At this point current starts rising sharply. Large reverse voltage and current generates excessive heat and destroys the device. If  $i_g > 0$  during reverse bias condition the reverse saturation current rises as explained in the previous section. This can be avoided by removing the gate current while the thyristor is reverse biased.

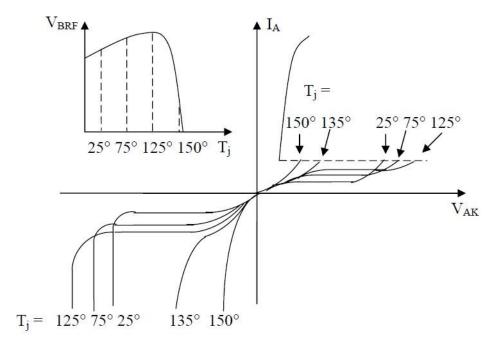

The static output i-v characteristics of a thyristor depends strongly on the junction temperature as shown in Fig 4.4.

Fig. 4.4: Effect of junction temperature  $(T_j)$  on the output i-v characteristics of a thyristor.

## **Dynamic characteristics**

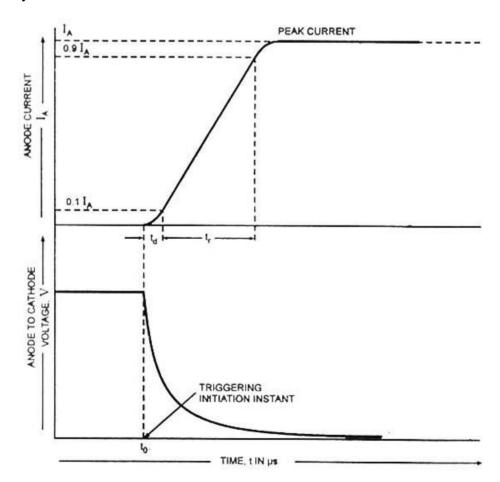

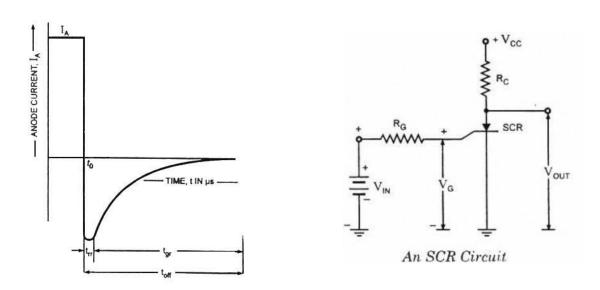

Turn-on and turn-off characteristics of an SCR are called the dynamic characteristics of the SCR.

## (a) Turn-On Characteristic.

The turn-on time characteristic shows the variation of current and voltage during turn-on. Turn-on time is defined as the time from the initiation of triggering, when the SCR offers infinite impedance to the flow of anode current, to the time when an equilibrium charge distribution is established throughout the device together with a steady state forward voltage drop. The turn-on time is about 1 to 3 micro seconds for the SCR readily available commercially.

The above Figure shows the form of current rise during the transition from the non-conducting to the fully conducting state. The time  $t_0$  indicate the initiation of turn-on which is caused by a step function of voltage applied to the gate. The period  $t_d$  is the delay time between the front of the gate pulse and the beginning of a rapid rate of increase of anode current. During the initial interval of turn-on  $(t_d)$  only a small area near the gate electrode conducts anode current.  $t_d$  is due to the charge build up time and decreases with the increase in

gate current. The rise time,  $\mathbf{t}_r$  depends on the speed at which charges build up to support the final anode current,  $I_A$ .  $\mathbf{t}_r$  is independent of gate current but depends upon the widths of base construction of SCR. The sum of  $\mathbf{t}_d$  and  $\mathbf{t}_c$  gives turn-on time  $\mathbf{t}_{on}$ . The turn-on time  $i_{on}$  depends on the anode circuit parameters, gate current amplitude and rise time. The turn-on time is important in pulse triggering.

#### (b) Turn-off Characteristic.

Turn-off means that all forward conduction has ceased and the re-application of a positive voltage to the anode will not cause flow of current without there being a gate signal. The turn-off characteristic is shown in figure. The time  $t_0$  indicates the instant of application of reverse voltage,  $t_{rr}$  is the duration for which the reverse recovery current flows after application of reverse voltage and t is the time required for the recombination of all excess carriers in the inner two layers of the device. The sum of time duration  $t_{rr}$  and time duration t gives the turn-off time  $t_{off}$ , that is  $t_{off} = t_{rr} + t_{gr}$ . At the end of turn-off time, a depletion layer gets developed across junction  $J_2$  and now SCR is capable of withstanding forward voltage. The turn-off time depends upon anode current, magnitude of reverse voltage and the rate of application of forward voltage.

# 1.2.4 Applications of SCR

#### 1. Power Control.

Because of the bistable characteristics of semiconductor devices, whereby they can be switched on and off, and the efficiency of gate control to trigger such devices, the SCRs are ideally suited for many industrial applications. SCRs have got specific advantages over

saturable core reactors and gas tubes owing to their compactness, reliability, low losses, and speedy turn-on and turn-off.

The bistable states (conducting and non-conducting) of the SCR and the property that enables fast transition from one state to the other are made use of in the control of power in both ac and decircuits.

#### 2. Switching.

Thyristor, being bistable device is widely used for switching of power signals owing to their long life, high operation speed and freedom from other defects associated with mechanical and electro-mechanical switches.

#### 3. Zero Voltage Switching.

In some ac circuits it is necessary to apply the voltage to the load when the instantaneous value of this voltage is going through the zero value. This is to avoid a high rate of increase of current in case of purely resistive loads such as lighting and furnace loads, and thereby reduce the generation of radio noise and hot-spot temperatures in the device carrying the load current.

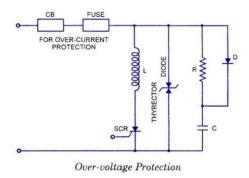

## 4. Over-Voltage Protection.

SCRs can be employed for protecting other equipment from over-voltages owing to their fast switching action. The SCR employed for protection is connected in parallel with the load. Whenever the voltage exceeds a specified limit, the gate of the SCR will get energized and trigger the SCR. A large current will be drawn from the supply mains and voltage across the load will be reduced. Two SCRs are used—one for the positive half-cycle and the other for negative half-cycle.

#### 5. Pulse Circuits.

SCRs are used for producing high voltage/current pulses of desired waveform and duration.

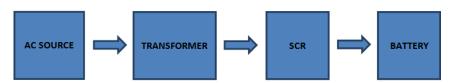

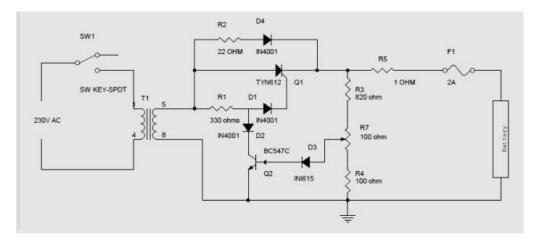

# 6. Battery Charging Regulator.

## **1.3 DIAC**

## 1.3.1 Operation, construction of DIAC and V-I characteristics curve

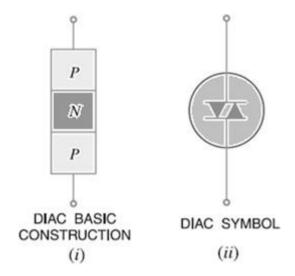

A diac is a two-terminal, three layer bidirectional device which can be switched from its OFF state to ON state for either polarity of applied voltage.

The diac can be constructed in either npn or pnp form. Fig. (i) shows the basic structure of a diac in pnp form. The two leads are connected to p-regions of silicon separated by an n-region. The structure of diac is very much similar to that of a transistor. However, there are several important differences:

- (i) There is no terminal attached to the base layer.

- (ii) The three regions are nearly identical in size.

- (iii) The doping concentrations are identical (unlike a bipolar transistor) to give the device symmetrical properties.

Fig. (ii) shows the symbol of a diac.

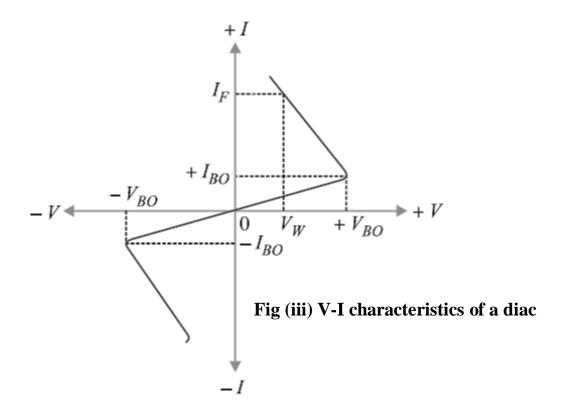

#### **Operation**

When a positive or negative voltage is applied across the terminals of a diac, only a small leakage current IBO will flow through the device. As the applied voltage is increased, the leakage current will continue to flow until the voltage reaches the breakover voltage VBO. At this point, avalanche breakdown of the reverse-biased junction occurs and the device exhibits negative resistance i.e. current through the device increases with the decreasing values of applied voltage. The voltage across the device then drops to \_breakback' voltage VW. Fig (iii) shows the V-I characteristics of a diac. For applied positive voltage less than + VBO and negative voltage less than – VBO, a small leakage current (± IBO) flows through the device. Under such conditions, the diac blocks the flow of current and effectively behaves

as an open circuit. The voltages + VBO and - VBO are the breakdown voltages and usually have a range of 30 to 50 volts.

When the positive or negative applied voltage is equal to or greater than the breakdown voltage, diac begins to conduct and the voltage drop across it becomes a few volts. Conduction then continues until the device current drops below its holding current. Note that the breakover voltage and holding current values are identical for the forward and reverse regions of operation. The DIAC can be used in many applications such as motor speed controls and light dimmers circuit.

# 1.3.2 Applications of DIAC

The **diacs**, because of their symmetrical bidirectional switching characteristics, are widely used as triggering devices in triac phase control circuits employed for lamp dimmer, heat control, universal motor speed control etc.

Although a **triac** may be fired into the conducting state by a simple resistive triggering circuit, but triggering devices are typically placed in series with the gates of SCRs and triacs as they give reliable and fast triggering. Diac is the most popular triggering device for the triac. This is illustrated in the following applications.

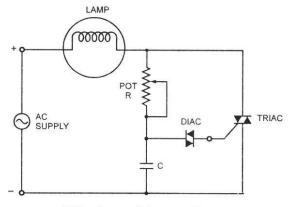

## 1. Triac Lamp Dimmer Circuit.

The circuit for a triac controlled by an R-C phase-shift network and a diac is given in figure. This circuit is an example of a simple lamp dimmer. The triac conduction angle is adjusted by adjusting the potentiometer R. The longer the triac conducts, the brighter the lamp will be. The diac acts like an open-circuit until the voltage across the capacitor exceeds its breakover or switching voltage (and the triac's required gate trigger voltage).

Triac Lamp Dimmer Circuit

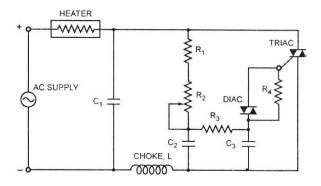

#### 2. Heat Control Circuit.

A typical diac-triac circuit used for smooth control of ac power to a heater is shown in figure. The capacitor  $C_1$  in series with choke L across the triac slows-up the voltage rise across the device during off-state. The resistor  $R_4$  across the diac ensures smooth control at all positions of potentiometer  $R_2$ . The triac conduction angle is adjusted by adjusting the potentiometer  $R_2$ . The longer the triac conducts, the larger the output will be from the heater. Thus a smooth control of the heat output from the heater is obtained.

(Heat Control Circuit using Diac)

## 1.4 TRIAC

# 1.4.1 Operation, construction of TRIAC and V-I characteristics curve

The Triac is a member of the thyristor family. But unlike a thyristor which conducts only in one direction (from anode to cathode) a triac can conduct in both directions. Thus a triac is similar to two back to back (anti parallel) connected thyristosr but with only three terminals.

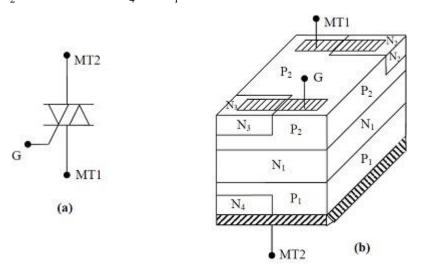

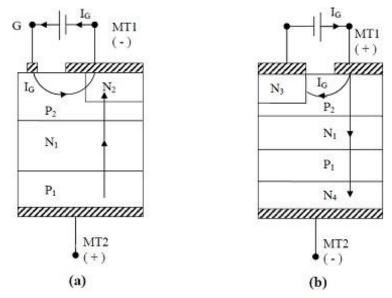

## Construction and operating principle

Fig. 5 (a) and (b) show the circuit symbol and schematic cross section of a triac respective. As the Triac can conduct in both the directions the terms -anode and -cathode are not used for Triacs. The three terminals are marked as MT (Main Terminal 1), MT (Main Terminal 2) and the gate by G. As shown in Fig 5 (b) the gate terminal is near MT and is connected to both

N and P regions by metallic contact. Similarly MT is connected to N and P regions while MT is connected to N and P regions.

Fig.5 Circuit symbol and schematic construction of a Triac

(a) Circuit symbol (b) Schematic construction.

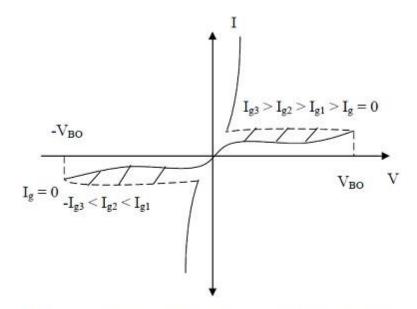

#### V-I characteristics

From a functional point of view a triac is similar to two thyristors connected in anti parallel. Therefore, it is expected that the V-I characteristics of Triac in the  $1^{\text{st}}$  and  $3^{\text{rd}}$  quadrant of the V-I plane will be similar to the forward characteristics of a thyristors. As shown in Fig. 6, with no signal to the gate the triac will block both half cycle of the applied ac voltage provided its peak value is lower than the break over voltage  $(V_{BO})$  of the device. However, the turning on of the triac can be controlled by applying the gate trigger pulse at the desired

instance. Mode-1 triggering is used in the first quadrant where as Mode-3 triggering is used in the third quadrant.

Fig. 6 : Steady state V - I characteristics of a Triac

As such, most of the thyristor characteristics apply to the triac (ie, latching and holding current). However, in a triac the two conducting paths (from MT<sub>1</sub> to MT<sub>2</sub> or from MT<sub>1</sub> to MT<sub>1</sub>) interact with each other in the structure of the triac. Therefore, the voltage, current and frequency ratings of triacs are considerably lower than thyristors. At present triacs with voltage and current ratings of 1200V and 300A (rms) are available. Triacs also have a larger on state voltage drop compared to a thyristor.

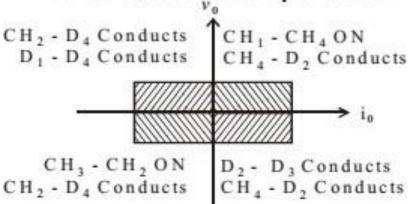

# 1.4.2 Modes of operation of TRIAC and mention the preferred modes

Since a Triac is a bidirectional device and can have its terminals at various combinations of positive and negative voltages, there are four possible electrode potential combinations as given below

- 1.  $MT_2$  positive with respect to  $MT_1$ , G positive with respect to  $MT_1$

- 2. MT<sub>2</sub> positive with respect to MT<sub>1</sub>, G negative with respect to MT<sub>1</sub>

- 3.  $MT_2$  negative with respect to  $MT_1$ , G negative with respect to  $MT_1$

- 4. MT<sub>2</sub> negative with respect to MT<sub>1</sub>, G positive with respect to MT<sub>1</sub>

The triggering sensitivity is highest with the combinations 1 and 3 and are generally used. However, for bidirectional control and uniforms gate trigger mode sometimes trigger

modes 2 and 3 are used. Trigger mode 4 is usually avoided. Fig 7 (a) and (b) explain the conduction mechanism of a triac in trigger modes 1 & 3 respectively.

Fig. 7 Conduction mechanism of a triac in trigger modes 1 and 3

(a) Mode – 1, (b) Mode – 3.

In trigger mode-1 the gate current flows mainly through the  $P_2$   $N_2$  junction like an ordinary thyristor. When the gate current has injected sufficient charge into  $P_2$  layer the triac starts conducting through the  $P_1$   $N_1$   $P_2$   $N_2$  layers like an ordinary thyristor.

In the trigger mode-3 the gate current  $I_g$  forward biases the  $P_2$   $P_3$  junction and a large number of electrons are introduced in the  $P_2$  region by  $N_3$ . Finally the structure  $P_2$   $N_1$   $P_1$   $N_4$  turns on completely.

# 1.4.3 Applications of TRIAC (Phase control using TRIAC)

A triac is functionally equivalent to two anti parallel connected thyristors. It can block voltages in both directions and conduct current in both directions.

- A triac has three terminals like a thyristor. It can be turned on in either half cycle by either a positive on a negative current pulse at the gate terminal.

- Triacs are extensively used at power frequency ac load (eg heater, light, motors) control applications.

## 1.5 Power BJT

## 1.5.1 Operation, construction of an NPN POWER Transistor as a switch

Power Bipolar Junction Transistor (BJT) is the first semiconductor device to allow full control over its Turn on and Turn off operations. It simplified the design of a large number of Power Electronic circuits that used forced commutated thyristors at that time and also helped realize a number of new circuits. BJT was the first semiconductor device to closely approximate an ideal fully controlled Power switch.

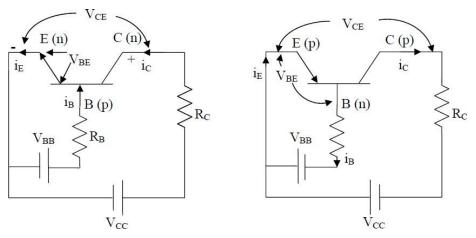

A junction transistor consists of a semiconductor crystal in which a **p** type region is sandwiched between two **n** type regions. This is called an **n-p-n** transistor. Alternatively an **n** type region may be placed in between two **p** type regions to give a **p-n-p** transistor. Fig above shows the circuit symbols and schematic representations of an **n-p-n** and a **p-n-p** transistor. The terminals of a transistor are called Emitter (E), Base (B) & Collector (C) as shown in the figure.

When a transistor is used as a controlled switch, the control current input is provided at the base terminal. The control circuit is connected between the base and emitter. The power terminals of the switch are the collector and the emitter.

The output characteristic is a plot of the current Ic through the switch versus the voltage VCE across it for a fixed value of the current  $I\Box$ .

Let us assume that  $V=150~V,~R=30\Omega$  and decide to keep  $I\Box$  at 0.6A. The voltage VCE across the switch and the current  $\emph{Ic}$  through it must be given by a point on the characteristic for  $I\Box=0.6~A$ . To locate this point, we used a second relationship by a straight line called the "load line."

$V_{CE} = V - I_C R = 150V - I_C \cdot 30\Omega$

What will happen if we progressively reduce the base current  $I_B$ .

| IB    | IC  | VCE           | PDIS=VCE IC |

|-------|-----|---------------|-------------|

| 0.6 A | ≈5A | VCE(SAT)≈2.5V | 12.5W       |

| 0.4 A | ≈5A | VCE(SAT)≈2.5V | 12.5W       |

| 0.2 A | 3A  | 60 V          | 180W        |

For  $I_B = 0.2$  A, the intersection point gives VCE = 60 V and a current of 3 A. The transistor is no longer in the saturated ON state. Such a condition is to be avoided, because, there is excessive power dissipation in the transistor (180W), which can result in its damage.

It is necessary to ensure a saturated ON state, by providing adequate base drive current, for the safe and satisfactory operation of the switch. Therefore, the minimum base current to ensure the saturated ON state is given by IB=IC/hFE where hFE is a parameter specified in the data sheet of the transistor.

Often it will be advisable to use a somewhat higher value of base current than that indicated by the above formula, as a safety feature, to take care of possible increases in *Ic* above the anticipated value.

# 1.5.2 Applications of BJT in Power switching applications

There are two types of **applications of BJT**, switching and amplification.

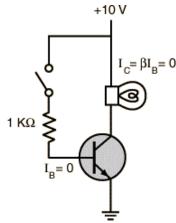

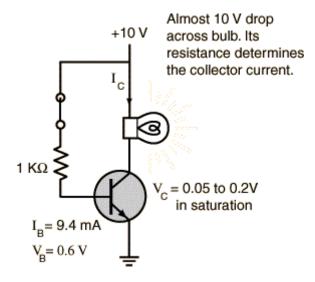

## Transistor as a Switch

For switching applications transistor is biased to operate in the saturation or cutoff region. Transistor in cutoff region will act as an open switching whereas in saturation will act as a closed switch.

## **Open Switch**

In the cutoff region (both junctions are reversed biased) the voltage across the CE junction is very high. The input voltage is zero so both base and collector currents are zero, hence the resistance offered by the BJT is very high (ideally infinite).

#### **Closed Switch**

In saturation (both junctions are forward biased) a high input voltage is applied to the base. The value of base resistance is adjusted such that a large base current flows. There is a small voltage drop across the collector emitter junction of the order of 0.05 to 0.2V and collector current is very large. A very small voltage drop takes place across the BJT and it can be said to be equivalent to a closed switch.

## 1.6 Power MOSFET

# Operation, construction of Power MOSFET & its characteristics curve

Power MOSFET is a device that evolved from MOS integrated circuit technology. The first attempts to develop high voltage MOSFETs were by redesigning lateral MOSFET to increase their voltage blocking capacity.

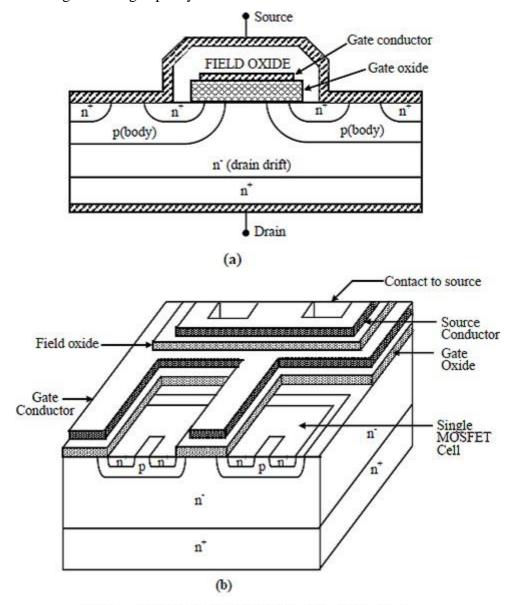

Fig. 8 Schematic construction of a power MOSFET (a) Construction of a single cell.

- (b) Arrangement of cells in a device.

The resulting technology was called lateral double deffused MOS (DMOS). However it was soon realized that much larger breakdown voltage and current ratings could be achieved by resorting to a vertically oriented structure. Since then, vertical DMOS (VDMOS) structure has been adapted by virtually all manufacturers of Power MOSFET. A power MOSFET using

VDMOS technology has vertically oriented three layer structure of alternating **p** type and **n** type semiconductors as shown in Fig 8 (a) which is the schematic representation of a single MOSFET cell structure. A large number of such cells are connected in parallel (as shown in Fig 8 (b)) to form a complete device

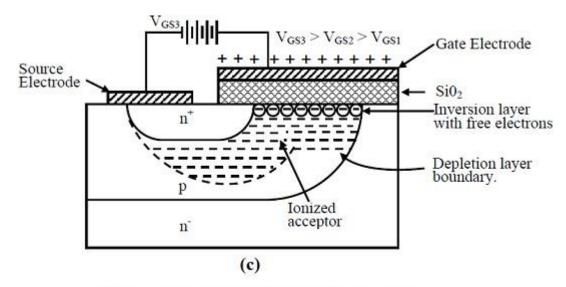

## **Operation**

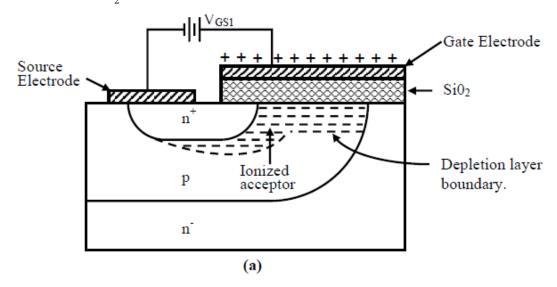

The gate region of a MOSFET which is composed of the gate metallization, the gate (silicon) oxide layer and the p-body silicon forms a high quality capacitor. When a small voltage is application to this capacitor structure with gate terminal positive with respect to the source (note that body and source are shorted) a depletion region forms at the interface between the  $SiO_2$  and the silicon as shown in Fig 9 (a).

Fig. 9 Gate control of MOSFET conduction.

- (a) Depletion layer formation;

- (b) Free electron accumulation;

- (c) Formation of inversion layer.

The positive charge induced on the gate metallization repels the majority hole carriers from the interface region between the gate oxide and the  $\mathbf{p}$  type body. This exposes the negatively charged acceptors and a depletion region is created.

Further increase in  $V_{GS}$  causes the depletion layer to grow in thickness. At the same time the electric field at the oxide-silicon interface gets larger and begins to attract free electrons as shown in Fig 9 (b). The immediate source of electron is electron-hole generation by thermal ionization. The holes are repelled into the semiconductor bulk ahead of the depletion region. The extra holes are neutralized by electrons from the source.

As  $V_{GS}$  increases further the density of free electrons at the interface becomes equal to the free hole density in the bulk of the body region beyond the depletion layer. The layer of free electrons at the interface is called the inversion layer and is shown in Fig 9 (c). The inversion layer has all the properties of an  $\mathbf{n}$  type semiconductor and is a conductive path or -channel between the drain and the source which permits flow of current between the drain and the source. Since current conduction in this device takes place through an  $\mathbf{n}$ - type -channel created by the electric field due to gate source voltage it is called -Enhancement type n-channel MOSFET.

The value of  $V_{GS}$  at which the inversion layer is considered to have formed is called the -Gate – Source threshold voltage  $V_{GS}$  (th)  $\parallel$ . As  $V_{GS}$  is increased beyond  $V_{GS}$ (th) the inversion layer gets somewhat thicker and more conductive, since the density of free electrons

increases further with increase in  $V_{GS}$ . The inversion layer screens the depletion layer adjacent to it from increasing  $V_{GS}$ . The depletion layer thickness now remains constant.

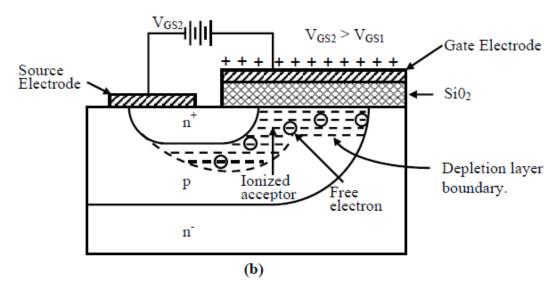

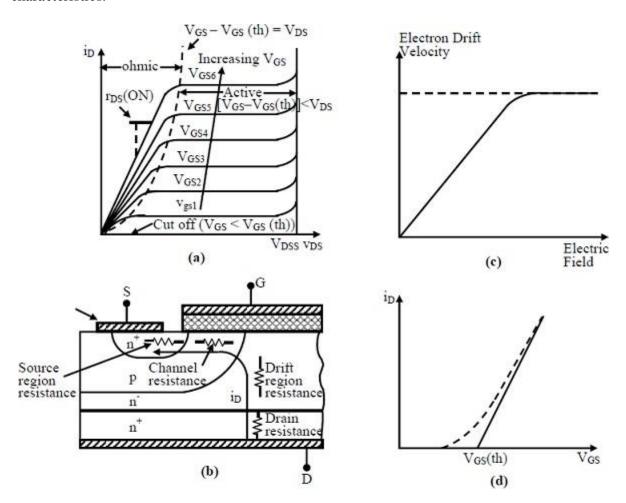

## Steady state output i-v characteristics of a MOSFET

The MOSFET, like the BJT is a three terminal device where the voltage on the gate terminal controls the flow of current between the output terminals, Source and Drain. The source terminal is common between the input and the output of a MOSFET. The output characteristics of a MOSFET is then a plot of drain current  $(i_D)$  as a function of the Drain – Source voltage  $(v_{DS})$  with gate source voltage  $(v_{DS})$  as a parameter. Fig 10 (a) shows such a characteristics.

Fig. 10 Output i-v characteristics of a Power MOSFET

- (a) i-v characteristics;

- (b) Components of ON-state resistance;

- (c) Electron drift velocity vs Electric field;

- (d) Transfer

With gate-source voltage  $(V_{GS})$  below the threshold voltage  $(v_{GS})$  the MOSFET operates in the cut-off mode. No drain current flows in this mode and the applied drain—source voltage  $(v_{DS})$  is supported by the body-collector **p-n** junction. Therefore, the maximum applied voltage should be below the avalanche break down voltage of this junction  $(V_{DSS})$  to avoid destruction of the device.

When  $V_{GS}$  is increased beyond  $v_{GS}$  (th) drain current starts flowing. For small values of  $v_{DS}$  ( $v_{DS} < (v_{GS} - v_{GS}(th))$   $i_D$  is almost proportional to  $v_{DS}$ . Consequently this mode of operation is called -ohmic mode of operation. In power electronic applications a MOSFET is operated either in the cut off or in the ohmic mode. The slope of the  $v_{DS} - i_D$  characteristics in this mode is called the ON state resistance of the MOSFET ( $r_{DS}$  (ON)). Several physical resistances as shown in Fig 10 (b) contribute to  $r_{DS}$  (ON). Note that  $r_{DS}$  (ON) reduces with increase in  $v_{GS}$ . This is mainly due to reduction of the channel resistance at higher value of

$v_{GS}$ . Hence, it is desirable in power electronic applications, to use as large a gate-source voltage as possible subject to the dielectric break down limit of the gate-oxide layer.

# 1.6.2 Applications of MOSFET

# 1MOSFET as an analog switch

Enhancement mode MOSFET based analog switches use the transistor channel as a low resistance to pass analog signals when on, and as a high impedance when off. Signals can flow in either direction across a MOSFET switch. In this application the drain and source of a MOSFET exchange places depending on the voltages of each electrode compared to that of the gate and the direction of current flow. For a simple MOSFET without an integrated diode from source to drain (or the back gate or body terminal tied to the source), the source is the more negative side for an NMOS or the more positive side for a PMOS. All of these switches are limited as to what signals they can pass when on or block when off by their gate-source, gate-drain and source-drain voltages, and source-to-drain currents; exceeding these voltage or current limits will potentially damage the switch.

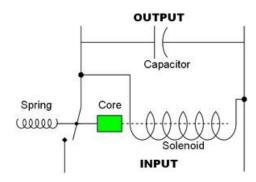

## 2 Switched Capacitor Circuits

A switched capacitor is an electronic circuit element used in discrete time signal processing systems. It works by transferring charge into and out of a capacitor when switches are opened and closed. Usually, non-overlapping signals are used to control the switches, often termed Break before Make switching, so that all switches are open for a very short time during the switching transitions. Discrete time filters implemented with these elements are termed 'switched-capacitor filters'. Unlike continuous time analog filters, which must be constructed with resistors, capacitors and sometimes inductors whose values are accurately known, switched capacitor filters depend only on the ratios between capacitances and the switching frequency. This makes them much more suitable for use within integrated circuits, where the accurately specified absolute value of components such as resistors and capacitors are not economical to construct.

## 1.7 GTO

# 1.7.1 Construction, operation of GTO and V-I characteristics

## Construction

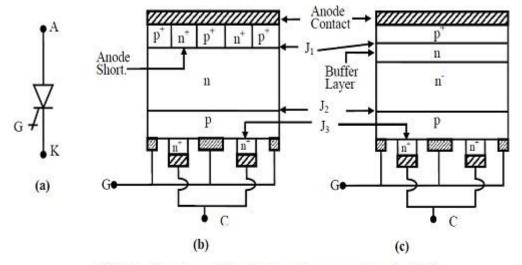

Fig. 11 Circuit symbol and schematic cross section of a GTO

(a) Circuit Symbol, (b) Anode shorted GTO structure,

(c) Buffer layer GTO structure.

Like a thyristor, a GTO is also a four layer three junction **p-n-p-n** device. In order to obtain high emitter efficiency at the cathode end, the **n** cathode layer is highly doped. Consequently, the break down voltage of the function  $J_3$  is low (typically 20-40V). The **p** type gate region has conflicting doping requirement. To maintain good emitter efficiency the doping level of this layer should be low, on the other hand, from the point of view of good turn off properties, resistively of this layer should be as low as possible requiring the doping level of this region to be high. Therefore, the doping level of this layer is highly graded. Additionally, in order to optimize current turn off capability, the gate cathode junction must be highly interdigitated. A 3000 Amp GTO may be composed of upto 3000 individual cathode segments which are a accessed via a common contact. The most popular design features multiple segments arranged in concentric rings around the device center.

The maximum forward blocking voltage of the device is determined by the doping level and the thickness of the  $\mathbf{n}$  type base region next. In order to block several kv of forward voltage the doping level of this layer is kept relatively low while its thickness is made considerably higher (a few hundred microns). Byond the maximum allowable forward voltage either the electric field at the main junction  $(J_2)$  exceeds a critical value (avalanche break

down) or the **n** base fully depletes, allowing its electric field to touch the anode emitter (punch through).

The junction between the  $\mathbf{n}$  base and  $\mathbf{p}+$  anode  $(J_1)$  is called the -anode junction $\|$ . For good turn on properties the efficiency of this anode junction should be as high as possible requiring a heavily doped  $\mathbf{p}+$  anode region. However, turn off capability of such a GTO will be poor with very low maximum turn off current and high losses. There are two basic approaches to solve this problem.

In the first method, heavily doped  $\mathbf{n}+$  layers are introduced into the  $\mathbf{p}+$  anode layer. They make contact with the same anode metallic contact. Therefore, electrons traveling through the base can directly reach the anode metal contact without causing hole injection from the  $\mathbf{p}+$  anode. This is the classic -anode shorted GTO structure as shown in Fig 11 (b). Due to presence of these -anode shorts the reverse voltage blocking capacity of GTO reduces to the reverse break down

Voltage of junction  $J_3$  (20-40 volts maximum). In addition a large number of -anode shorts reduces the efficiency of the anode junction and degrades the turn on performance of the device. Therefore, the density of the -anode shorts are to be chosen by a careful compromise between the turn on and turn off performance.

## **Operating principle of a GTO**

GTO being a monolithic **p-n-p-n** structure just like a thryistor its basic operating principle can be explained in a manner similar to that of a thyristor. In particular, the **p-n-p-n** structure of a GTO can be thought of consisting of one **p-n-p** and one **n-p-n** transistor connected in the regenerative configuration as shown in Fig 12.

From the -two transistor analogy (Fig 12 (a)) of the GTO structure one can write.

$$i_{C1} = \infty_{p} I_{A} + I_{CBO1}$$

$$i_{B1} = i_{C2} = \infty_{n} I_{k} + I_{CBO2}$$

$$I_{k} = I_{A} + I_{G} \text{ and } I_{A} = i_{B1} + i_{C1}$$

$$I_{A} = \frac{\infty_{n} I_{G} + (i_{CBO1} + i_{CBO2})}{1 - (\infty_{n} + \infty_{p})}$$

(5.1)

$$(5.2)$$

With applied forward voltage  $V_{AK}$  less than the forward break over voltage both  $I_{CBO1}$  and  $I_{CBO2}$  are small. Further if  $I_{G}$  is zero  $I_{A}$  is only slightly higher than  $(I_{CBO1} + I_{CBO2})$ . Under this condition both a and a are small and (a + a) < 1. The device is said to be in the forward blocking mode.

Fig12 Current distribution in a GTO

(a) During turn on; (b) During turn off.

To turn the device on either the anode voltage can be raised until I CBO1 and I CBO2 increases by avalanche multiplication process or by injecting a gate current. The current gain a of silicon transistors rises rapidly as the emitter current increases. Therefore, any mechanism which causes a momentary increase in the emitter current can be used to turn on the device. Normally, this is done by injecting current into the p base region via the external gate contract. As  $a_n + a_p$  approaches unity the anode current tends to infinity. Physically as  $a_n + a_p$  nears unity the device starts to regenerate and each transistor drives its companion into saturation. Once in saturation, all junctions assume a forward bias and total potential drop across the device becomes approximately equal to that of a single **p-n** diode. The anode current is restricted only by the external circuit. Once the device has been turned on in this manner, the external gate current is no longer required to maintain conduction, since the regeneration process is self-sustaining. Reversion to the blocking mode occurs only when the anode current is brought below the -holding current level.

To turn off a conducting GTO the gate terminal is biased negative with respect to the cathode. The holes injected from the anode are, therefore, extracted from the p base through the gate metallization into the gate terminal (Fig 12 (b)). The resultant voltage drop in the  $\bf p$  base above the  $\bf n$  emitter starts reverse biasing the junction  $\bf J_3$  and electron injection stops here.

The process originates at the periphery of the  $\bf p$  base and the  $\bf n$  emitter segments and the area still injecting electron shrinks. The anode current is crowded into higher and higher density filaments in most remote areas from the gate contact. This is the most critical phase in the GTO turn off process since highly localized high temperature regions can cause device failure unless these current filaments are quickly extinguished. When the last filament disappears, electron injection stops completely and depletion layer starts to grow on both  $\bf J_2$  and  $\bf J_3$ . At this point the device once again starts blocking forward voltage. However, although the cathode current has ceased the anode to gate current continues to flow (Fig 12 (b)) as the  $\bf n$  base excess carriers diffuse towards  $\bf J_1$ . This -tail current|| then decays exponentially as the  $\bf n$  base excess carriers reduce by recombination. Once the tail current has completely disappeared does the device regain its steady state blocking characteristics. -Anode Shorts|| (or transparent emitter) helps reduce the tail current faster by providing an alternate path to the  $\bf n$  base electrons to reach the anode contact without causing appreciable hole injection from anode.

## Steady state output and gate characteristics

Fig. 13 Steady state characteristics of a GTO

(a) Output characteristics; (b) Gate characteristics.

This characteristic in the first quadrant is very similar to that of a thyristor as shown in Fig. 13 (a). However, the latching current of a GTO is considerably higher than a thyristor of similar rating. The forward leakage current is also considerably higher. In fact, if the gate current is not sufficient to turn on a GTO it operates as a high voltage low gain transistor with considerable anode current. It should be noted that a GTO can block rated forward voltage only when the gate is negatively biased with respect to the cathode during forward blocking state. At least, a low value resistance must be connected across the gate cathode terminal. Increasing the value of this resistance reduces the forward blocking voltage of the GTO. Asymmetric GTOs have small (20-30 V) reverse break down voltage. This may lead the device to operate in -reverse avalanche under certain conditions. This condition is not dangerous for the GTO provided the avalanche time and current are small. The gate voltage during this period must remain negative.

Fig 13 (b) shows the gate characteristics of a GTO. The zone between the min and max curves reflects parameter variation between individual GTOs. These characteristics are valid for DC and low frequency AC gate currents.

# 1.7.2 Application of GTO

The main applications are in variable speed motor drives, high power inverters, static VAR compensators (SVCs) and AC/DC power supplies with high power ratings and traction. GTOs are increasingly being replaced by integrated gate-commutated thyristors, which are an evolutionary development of the GTO, and insulated gate bipolar transistors, which are members of the transistor family.

## **1.8 IGBT**

# 1.8.1 Operation, construction of IGBT and its characteristics curve

## **Constructional Features of an IGBT**

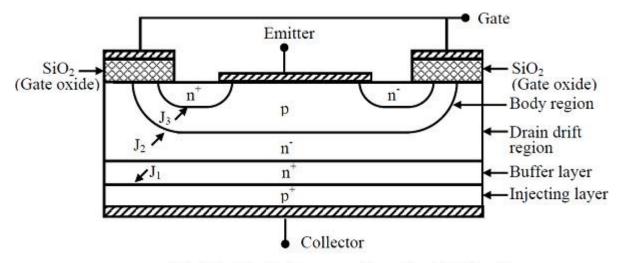

Vertical cross section of a n channel IGBT cell is shown in Fig 14. Although p channel IGBTs are possible n channel devices are more common

Fig. 14 Vertical cross section of an IGBT cell.

The major difference with the corresponding MOSFET cell structure lies in the addition of a **p**+ injecting layer. This layer forms a **pn** junction with the drain layer and injects minority carriers into it. The **n** type drain layer itself may have two different doping levels. The lightly doped n- region is called the drain drift region. Doping level and width of this layer sets the forward blocking voltage (determined by the reverse break down voltage of J<sub>2</sub>) of the device. However, it does not affect the on state voltage drop of the device due to conductivity modulation as discussed in connection with the power diode. This construction of the device is called -Punch Trough (PT) design. The Non-Punch Through (NPT) construction does not have this added n+ buffer layer. The PT construction does offer lower on state voltage drop compared to the NPT construction particularly for lower voltage rated devices. However, it does so at the cost of lower reverse break down voltage for the device, since the reverse break down voltage of the junction J<sub>1</sub> is small. The rest of the construction of the device is very similar to that of a vertical MOSFET including the insulated gate structure and the shorted body (p type) – emitter (n+ type) structure. The doping level and physical geometry of the **p** type body region however, is considerably different from that of a MOSFET in order to defeat the latch up action of a parasitic thyristor embedded in the IGBT

structure. A large number of basic cells as shown in Fig 14 are grown on a single silicon wafer and connected in parallel to form a complete IGBT device.

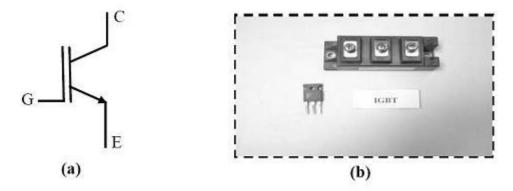

Fig. 15 Circuit symbol of an IGBT.

- (a) Circuit symbol.

- (b) Photograph.

## Operating principle of an IGBT

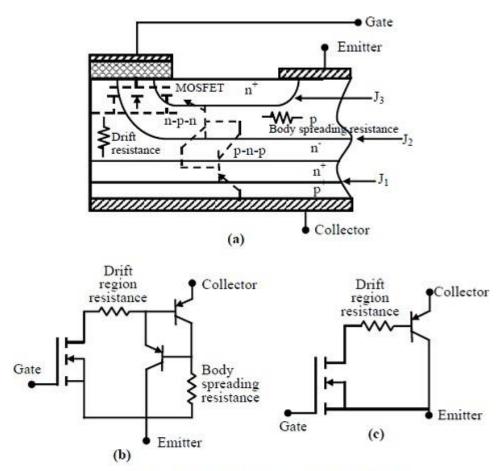

Operating principle of an IGBT can be explained in terms of the schematic cell structure and equivalent circuit of Fig 16(a) and (c). From the input side the IGBT behaves essentially as a MOSFET. Therefore, when the gate emitter voltage is less than the threshold voltage no inversion layer is formed in the  $\bf p$  type body region and the device is in the off state. The forward voltage applied between the collector and the emitter drops almost entirely across the junction  $\bf J_2$ . Very small leakage current flows through the device under this condition. In terms of the equivalent current of Fig 16(c), when the gate emitter voltage is lower than the threshold voltage the driving MOSFET of the Darlington configuration remains off and hence the output  $\bf p$ - $\bf n$ - $\bf p$  transistor also remains off.

When the gate emitter voltage exceeds the threshold, an inversion layer forms in the **p** type body region under the gate. This inversion layer (channel) shorts the emitter and the drain drift layer and an electron current flows from the emitter through this channel to the drain drift region. This in turn causes substantial hole injection from the **p**+ type collector to the drain drift region. A portion of these holes recombine with the electrons arriving at the drain drift region through the channel. The rest of the holes cross the drift region to reach the p type body where they are collected by the source metallization.

From the above discussion it is clear that the n type drain drift region acts as the base of the output **p-n-p** transistor. The doping level and the thickness of this layer determines the current gain  $-a \parallel$  of the **p-n-p** transistor. This is intentionally kept low so that most of the device current flows through the MOSFET and not the output **p-n-p** transistor collector. This

helps to reduced the voltage drop across the -body|| spreading resistance shown in Fig 16 (b) and eliminate the possibility of static latch up of the IGBT.

Fig.16 Parasitic thyristor in an IGBT cell.

- (a) Schematic structure

- (b) Exact equivalent circuit.

- (c) Approximate equivalent circuit

The total on state voltage drop across a conducting IGBT has three components. The voltage drop across  $J_1$  follows the usual exponential law of a **pn** junction. The next component of the voltage drop is due to the drain drift region resistance. This component in an IGBT is considerably lower compared to a MOSFET due to strong conductivity modulation by the injected minority carriers from the collector. This is the main reason for reduced voltage drop across an IGBT compared to an equivalent MOSFET. The last component of the voltage drop across an IGBT is due to the channel resistance and its magnitude is equal to that of a comparable MOSFET.

## Steady state characteristics of an IGBT

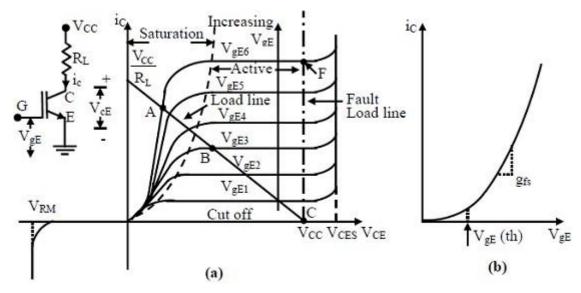

The i-v characteristics of an n channel IGBT is shown in Fig 17 (a). They appear qualitatively similar to those of a logic level BJT except that the controlling parameter is not a base current but the gate-emitter voltage.

Fig. 17 Static characteristics of an IGBT

(a) Output characteristics; (b) Transfer characteristics

When the gate emitter voltage is below the threshold voltage only a very small leakage current flows though the device while the collector – emitter voltage almost equals the supply voltage (point C in Fig 17(a)). The device, under this condition is said to be operating in the cut off region. The maximum forward voltage the device can withstand in this mode (marked  $V_{CES}$  in Fig 17 (a)) is determined by the avalanche break down voltage of the body – drain **p-n** junction. Unlike a BJT, however, this break down voltage is independent of the collector current as shown in Fig 17(a). IGBTs of Non-punch through design can block a maximum reverse voltage ( $V_{RM}$ ) equal to  $V_{CES}$  in the cut off mode. However, for Punch Through IGBTs  $V_{RM}$  is negligible due to the presence of the heavily doped **n**+ drain buffer layer.

As the gate emitter voltage increases beyond the threshold voltage the IGBT enters into the active region of operation. In this mode, the collector current  $i_c$  is determined by the transfer characteristics of the device as shown in Fig 17(b). This characteristic is qualitatively similar to that of a power MOSFET and is reasonably linear over most of the collector current range. The ratio of  $i_c$  to  $(V_{gE} - v_{gE(th)})$  is called the forward transconductance  $(g_{fs})$  of the device and is an important parameter in the gate drive circuit design. The collector emitter voltage, on the other hand, is determined by the external load line ABC as shown in Fig 17(a).

As the gate emitter voltage is increased further i also increases and for a given load resistance ( $R_L$ )  $v_{CE}$  decreases. At one point  $v_{CE}$  becomes less than  $vgE - v_{gE}$  (th). Under this condition the driving MOSFET part of the IGBT (Fig 16(c)) enters into the ohmic region and drives the output **p-n-p** transistor to saturation. Under this condition the device is said to be in the saturation mode. In the saturation mode the voltage drop across the IGBT remains almost constant reducing only slightly with increasing  $v_{oE}$ .

In power electronic applications an IGBT is operated either in the cut off or in the saturation region of the output characteristics. Since  $v_{CE}$  decreases with increasing  $v_{gE}$ , it is desirable to use the maximum permissible value of  $v_{gE}$  in the ON state of the device.  $v_{gE}(Max)$  is limited by the maximum collector current that should be permitted to flow in the IGBT as dictated by the -latch-upll condition discussed earlier. Limiting  $V_{gE}$  also helps to limit the fault current through the device. If a short circuit fault occurs in the load resistance  $R_{L}$  (shown in the inset of Fig 17(a)) the fault load line is given by CF. Limiting  $v_{gE}$  to  $v_{gE6}$  restricts the fault current corresponding to the operating point F. Most IGBTs are designed to with stand this fault current for a few microseconds within which the device must be turned off to prevent destruction of the device.

## **1.8.2** Applications of IGBT: IGBTs are used in high power applications such as:

- Appliance motor drives

- Electric vehicle motor drives

- Power factor correction converters

- Uninterruptible power supplies

- Solar inverters

- High frequency welders

- Inductive heating cookers

# **Chapter – 2 SCR CONTROL CIRCUITS**

SCR or silicon controlled rectifier is a controlled device and it behaves as a short circuit while in the on state and as open circuit when in off condition.

#### 2.1 Turn On Methods

## 2.1.1 Describe briefly different methods of TURN ON of an SCR

Turn-on method is otherwise known as triggering method. The turning on Process of the SCR is known as Triggering. In other words, turning the SCR from Forward-Blocking state to Forward-Conduction state is known as Triggering.

The various SCR triggering methods are

- Forward Voltage Triggering

- Thermal or Temperature Triggering

- Radiation or Light triggering

- dv/dt Triggering

- Gate Triggering

#### (a) Forward Voltage Triggering:-

In this mode, an additional forward voltage is applied between anode and cathode. When the anode terminal is positive with respect to cathode  $(V_{AK})$ , Junction  $J_1$  and  $J_3$  is forward biased and junction  $J_2$  is reverse biased. No current flows due to depletion region in  $J_2$  is reverse biased (except leakage current). As  $V_{AK}$  is further increased, at a voltage  $V_{BO}$  (Forward Break Over Voltage) the junction  $J_2$  undergoes avalanche breakdown and so a current flows and the device tends to turn ON (even when gate is open)

#### (b) Thermal (or) Temperature Triggering:-

The width of depletion layer of SCR decreases with increase injunction temperature. Therefore in SCR when  $V_{AR}$  is very near its breakdown voltage, the device is triggered by increasing the junction temperature. By increasing the junction temperature the reverse biased junction collapses thus the device starts to conduct.

#### (c) Radiation Triggering (or) Light Triggering:-

For light triggered SCRs a special terminal niche is made inside the inner P layer instead of gate terminal. When light is allowed to strike this terminal, free charge carriers are generated. When intensity of light becomes more than a normal value, the thyristor starts conducting. This type of SCRs are called as LASCR

#### (d) dv/dt Triggering:-

When the device is forward biased,  $J_1$  and  $J_3$  are forward biased,  $J_2$  is reverse biased. Junction  $J_2$  behaves as a capacitor, due to the charges existing across the junction. If voltage across the device is V, the charge by Q and capacitance by C then,

$$\begin{split} &i_c \!\!=\!\! dQ/dt \\ &Q \!\!=\!\! CV \\ &i_c \!\!=\!\! d(CV)/dt =\!\! C.dV/dt \!\!+\!\! V.dC/dt \\ &As\ dC/dt = 0,\, i_c = C.dV/dt \end{split}$$

Therefore when the rate of change of voltage across the device becomes large, the device may turn ON, even if the voltage across the device is small.

#### (e) Gate Triggering:-

This is most widely used SCR triggering method. Applying a positive voltage between gate and cathode can Turn ON a forward biased thyristor. When a positive voltage is applied at the gate terminal, charge carriers are injected in the inner P-layer, thereby reducing the depletion layer thickness. As the applied voltage increases, the carrier injection increases, therefore the voltage at which forward break-over occurs decreases.

## 2.1.2 General functions to be fulfilled by gate control circuits

The gate control circuit is also called the firing circuit and a firing circuit should fulfill the following two functions.

(i) If power circuit has more than one SCR, the firing circuit should produce gating pulses for each SCR at the desired instant for proper operation of the power circuit.

These pulses must be periodic in nature and the sequence of firing must correspond with the type of thyristorised power controller.

(ii) Before giving the voltage pulses to the firing circuit, the voltage pulses should be fed to a driver circuit. The reason is that the control signal generated by a firing circuit may not be able to turn-on the SCR.

# 2.2 Firing Circuits

## 2.2.1 General layout diagram of firing circuit

The different firing circuits used are

- R-firing circuit

- RC-firing circuit

- UJT pulse trigger circuit

- Synchronous triggering (Ramp Triggering ) circuit

#### 2.2.2R firing circuits or Resistance triggering circuit:

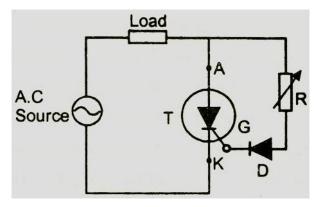

The following circuit shows the resistance triggering. In this method, the variable resistance R is used to control the gate current.

Depending upon the value of R, when the magnitude of the gate current reaches the sufficient value(latching current of the device) the SCR starts to conduct. The diode D is called as blocking diode. It prevents the gate cathode junction from getting damaged in the negative half cycle. By considering that the gate circuit is purely resistive, the gate current is in phase with the applied voltage. By using this method we can achieve maximum firing angle up to  $90^{\circ}$ .

## 2.2.3RC-firing circuit

The following circuit shows the resistance-capacitance triggering.

By using this method we can achieve firing angle more than 90°. In the positive half cycle, the capacitor is charged through the variable resistance R up to the peak value of the applied voltage. The variable resistor R controls the charging time of the capacitor. Depends upon the voltage across the capacitor, when sufficient amount of gate current will flow in the circuit, the SCR starts to conduct. In the negative half cycle, the capacitor C is charged up to the negative peak value through the diode D2. Diode D1 is used to prevent the reverse break down of the gate cathode junction in the negative half cycle.

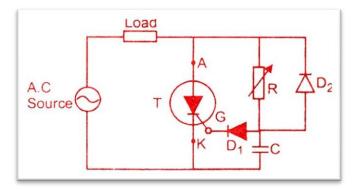

## 2.2.4UJT pulse trigger circuit

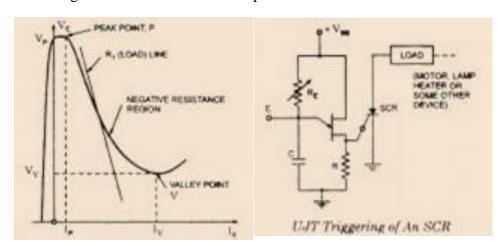

One common application of the Uni-junction transistor is the triggering of the other devices such as the SCR, triac etc. The basic elements of such a triggering circuit are shown in figure. The resistor  $R_E$  is chosen so that the load line determined by  $R_E$  passes through the device characteristic in the negative resistance region, that is, to the right of the peak point but to the left of the valley point, as shown in figure. If the load line does not pass to the right of the peak point P, the device cannot turn on.

For ensuring turn-on of UJT  $R_E < V_{BB} - Vp / I_P$

This can be established as below

Consider the peak point at which  $I_{RE} = Ip$  and  $V_E = V_P$

(the equality  $I_{RE} = I_P$  is valid because the charging current of capacitor, at this instant is zero, that is, the capacitor, at this particular instant, is changing from a charging state to a discharging state).

Then  $V_E = V_{BB} - I_{RE} R_E$

So,  $R_E(MAX) = V_{BB} - V_E / I_{RE} = V_{BB} - V_P / I_P$  at the peak point.

At the valley point, V

$I_E = I_V$  and  $V_E = V_V$  so that

$V_E = V_{BB} - I_{RE} R_E$

So  $R_E(MIN) = V_{BB} - V_E / I_{RE} = V_{BB} - V_V / I_V$  or for ensuring turn-off.

$R_E > \, \equiv V_{BB} - V_V / I_V$

So, the range of resistor R<sub>E</sub> is given as

$$V_{BB} - V_P \, / \, I_P \! > \! R_E \! > V_{BB} - V_V \, / \, I_V$$

The resistor R is chosen small enough so as to ensure that SCR is not turned on by voltage  $V_R$  when emitter terminal E is open or  $I_E = 0$

The voltage  $V_R = RV_{BB}/R + R_{BB}$  for open-emitter terminal.

The capacitor C determines the time interval between triggering pulses and the time duration of each pulse. By varying  $R_E$ , we can change the time constant  $R_E$  C and alter the point at which the UJT fires. This allows us to control the conduction angle of the SCR, which means the control of load current.

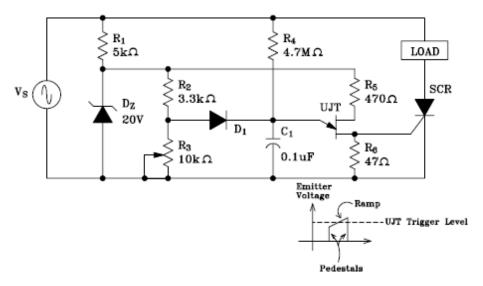

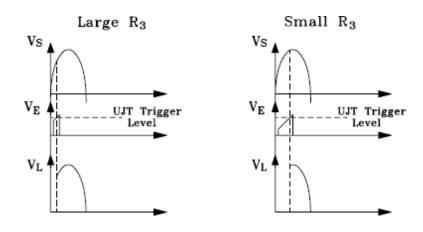

## 2.2.5 Ramp-Pedestal UJT-SCR Control Circuit:

The circuit, shown below, uses a UJT to trigger a SCR. The UJT is used to more accurately trigger the SCR. When the source voltage exceeds 20V, the zener diode  $(D_Z)$  will begin to conduct, applying a DC voltage across the base connections of the UJT. At the same time, diode  $D_1$  will be forward biased, and the capacitor will quickly charge through  $R_1$  and  $R_2$ . This represents the left-hand pedestal portion of the of the emitter voltage.

Once the capacitor charges to the voltage across  $R_3$ ,  $D_1$  will become reverse biased and the capacitor will continue to slowly charge through  $R_4$ . This represents the ramp portion of the emitter voltage.

The capacitor continues to charge until the UJT fires. At this point the capacitor will quickly discharge through  $R_6$ , and this represents the right-hand pedestal of the emitter voltage. The capacitor discharge is sufficient to trigger the SCR. The point at which the UJT fires can be adjusted by varying the pot R3. With a large setting on R3, the capacitor must charge to a larger value before D2 becomes reverse biased. This causes the UJT to fire faster, resulting in more of the source voltage appearing across the SCR. This can be seen graphically as shown in the fig.

## 2.3 Turn-off methods (Communication Schemes)

The term commutation basically means the transfer of current from one path to another. It is not possible for a thyristor to turn itself OFF; the circuit in which it is connected must reduce the thyristor current to zero to enable it to turn-off.

#### 2.3.1 Definition

**'COMMUTATION**' is the term to describe the methods of achieving this, or it is defined as the process of turning-off a thyristor.

## 2.3.2 List different types of communication methods

Broadly classified into two methods:

- 1. Natural commutation

- 2. Forced commutation

#### Natural commutation

This widely used method of commutation makes use of the alternating, reversing nature of a.c voltage to effect the current transfer. As the current passes through natural zero, a reverse voltage will simultaneously appear across the device. This immediately turns-off the device. This process is called as natural commutation since no external circuit is required for this purpose.

#### Forced commutation

In case of d.c circuits, for switching off the thyristors, the forward current should be forced to be zero by means of some external circuits. The process is called forced commutation.

#### Classification of forced commutation techniques

The classification is based on the arrangement of commutating components and the manner in which zero current is obtained in the SCR. The six distinct classes by which the SCR can be turned off are:

Class A Self commutated by a resonating load

Class B Self commutated by a L-C circuit

Class C C or L-C switched by another load carrying SCR otherwise known as Complementary commutation

Class D C or L-C switched by an auxiliary SCR, known as Auxiliary commutation

Class E An external pulse source for commutation, also known as External pulse commutation

Class F or AC line commutation or natural commutation

## 2.3.3 Different commutation with circuit diagram and waveforms

#### a) Line commutation or Class-F commutation

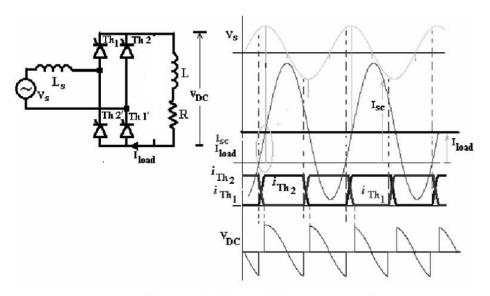

If the supply is an alternating voltage, load current will flow during the positive half cycle. With a highly inductive load, the current may remain continuous for some time till the energy trapped in the load inductance is dissipated. During the negative half cycle, therefore, the SCR will turn off when the load current becomes zero 'naturally'. The negative polarity of the voltage appearing across the outgoing SCR turns it off if the voltage persists for the rated turnoff period of the device. The duration of the half cycle must be definitely longer than the turnoff time of the SCR. The rectifier in the below figure is supplied from a single phase AC supply. The commutation process involved here is representative of that in a three phase converter. The converter has an input inductance L<sub>s</sub> arising mainly out of the leakage reactance of the supply transformer. Initially, SCRs Th<sub>1</sub>and Th<sub>1</sub> are considered to be conducting. The triggering angle for the converter is around  $60^{\circ}$ . The converter is operating in the continuous conduction mode aided by the highly-inductive load. When the incoming SCRs, Th2and Th2' are triggered, the current through the incoming devices cannot rise instantaneously to the load current level. A circulating current Isc builds up in the shortcircuited path including the supply voltage, Vs-Ls-Th<sub>1</sub>'- Th<sub>2</sub> and Vs- Ls-Th<sub>2</sub>'-Th<sub>1</sub> paths. The period when both the devices conduct is known as the 'overlap period'. Since all SCRs are in conduction, the output voltage for this period is zero. If the 'fully-controlled' converter in the figure is used as an inverter with triggering angles  $> 90^{\circ}$ , the converter triggering can be delayed till the 'margin angle' which includes the overlap angle and the turn-off time of the SCR - both dependent on the supply voltages.

Class F, natural commutation by supply voltage

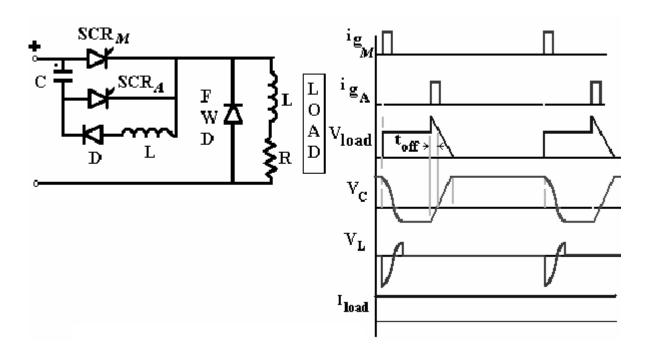

#### b) Auxiliary voltage commutation or Class-D commutation

The following circuit is used for auxiliary voltage commutation. SCR<sub>A</sub> must be triggered first in order to charge the upper terminal of the capacitor as positive. As soon as C is charged to the supply voltage, SCR<sub>A</sub> will turn off.

When SCR<sub>M</sub> is triggered the current flows in two paths:

- Load current flows through the load and

- The commutating current flows through C- SCR<sub>M</sub>-L-D network.

The charge on C is reversed and held at that level by the diode D. When  $SCR_A$  is retriggered, the voltage across C appears across  $SCR_M$  via  $SCR_A$  and  $SCR_M$  is turned off. If the load carries a constant current as in Fig. the capacitor again charges linearly to the dot as positive.

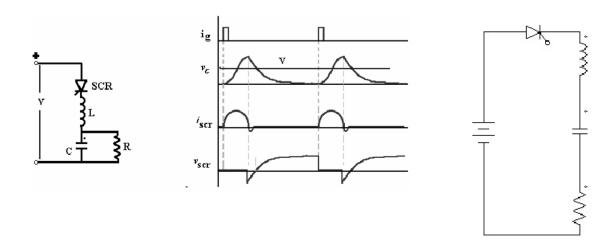

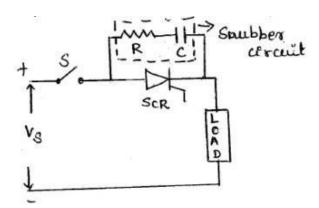

#### c) Resonant commutation or Class-A commutation

When the SCR is triggered, anode current flows and charges up C with the dot as positive. The L-C-R forms a second order under-damped circuit. The current through the SCR builds up and completes a half cycle. When the inductor current will then attempt to flow through the SCR in the reverse direction and the SCR will be turned off. Load can be either in parallel with capacitance or in series with the capacitance as in fig below. The capacitor voltage is at its peak when the SCR turns off and the capacitor discharges into the resistance in an exponential manner .The SCR is reverse-biased till the capacitor voltages returns to the level of the supply voltage V.

# **Chapter-3 CONTROLLED RECTIFIER**

#### Introduction

Single phase fully controlled bridge converters are widely used in many industrial applications. They can supply unidirectional current with both positive and negative voltage polarity. Thus they can operate either as a controlled rectifier or an inverter. The inverter mode of operation of a single phase fully controlled converter is made possible by the forward voltage blocking capability of the thyristors which allows the output voltage to go negative. The disadvantages of the single phase fully controlled converter are also related to the same capability.

### **Application**

Used in high voltage DC transmission, electrometallurgical process, magnetic power supplies, electroplating, battery charging, speed control of Dc drives, Traction.

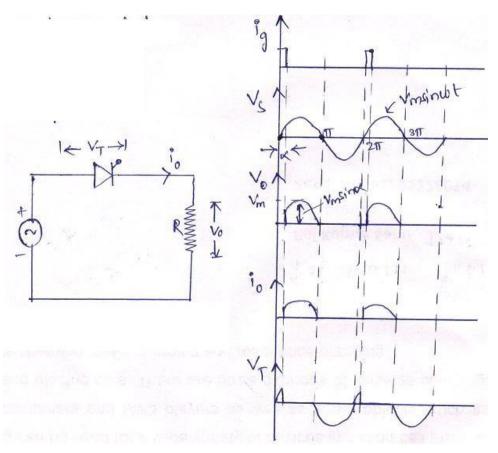

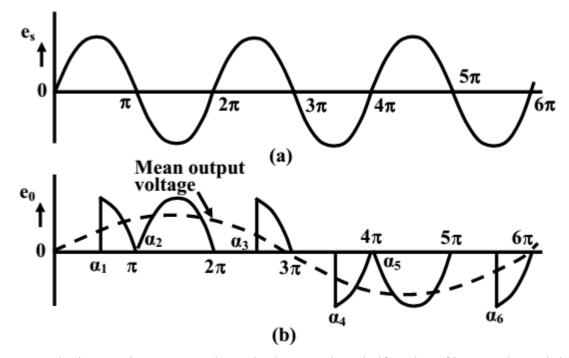

3.1 Controlled rectifiers Techniques (Phase Angle, Extinction Angle control & PWM) and 3.3 principle of phase control and definition of firing angle (alpha) and Conduction angle (beta) with schematic diagram and waveforms for half wave controlled rectifier

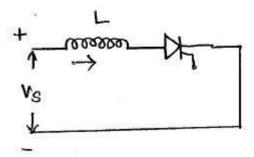

#### Principle of phase control

A simple controlled rectifier circuit consists of a single thyristor feeding dc power to a resistive load R. source voltage is  $v_s = v_m \sin wt$ .

An SCR can conduct only when anode voltage is positive and a gating signal is applied. A thyristor blocks the flow of load current io until it is triggered.

At some delay angle  $\alpha$ , a positive gate signal is applied between gate and cathode turns on the SCR. Immediately full supply voltage is applied to the load as  $v_o$ .

**Firing Angle(\alpha):** - It is the angle between the instant at which the thyristor would conduct, if it was a diode, and the instant at which it is triggered.

It can also be defined as the angle measured from the instant SCR gets forward biased to the instant it is triggered.

Conduction Angle( $\gamma$ ): - it is defined as the angle during the period in which the SCR is in conduction state.

**Extinction Angle(\beta)**: - it is the angle measured from the reference point to the instant at which the current extinguishes to zero.

Relation between  $\beta$ ,  $\gamma$  and  $\alpha$

$$\beta = \alpha + \gamma$$

#### 3.2 Classification of converters: -

The phase controlled converters may be classified as semi-converter, full converter, dual converter. Depending on the input ac supply used they are classified as single phase and three phase converters.

**Semi-converter:** -A semi-converter is a one quadrant converter and it has one polarity of output voltage and current. It contains a mixture of diodes and thyristors allowing more limited control over the dc output voltage level than the full controlled rectifier. It is cheaper. It permits power flow from AC system to DC load. It is also known as half-wave controlled converter.

**Full-converter:** -A full-converter is a two-quadrant converter and the polarity of its output voltage can be either positive or negative. However, the output current of full-converter has one polarity only. Here power can be transmitted from AC side to DC side (conversion) and from DC side to AC side (inversion). It uses only thyristor as rectifying elements.

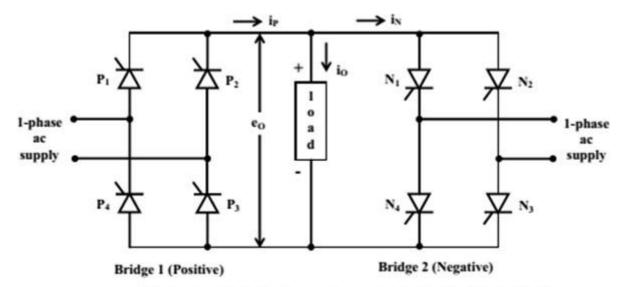

**Dual-converter:** -If two full converters are connected back to back they form a dual converter. It can operate in four quadrants and both the output voltage and current can be either positive or negative. Normally these are used in high power applications.

## 3.4 Integral Cycle Control (ICC)

For power transfer two types of controls are normally used. One is on-off control or integral cycle control and another is phase angle control.

In integral-cycle control, thyristor switches connect the load to the ac source for a few cycles of input voltage and disconnects it for another few cycles.

The ICC is otherwise known as burst firing or zero voltage switching or cycle selection.

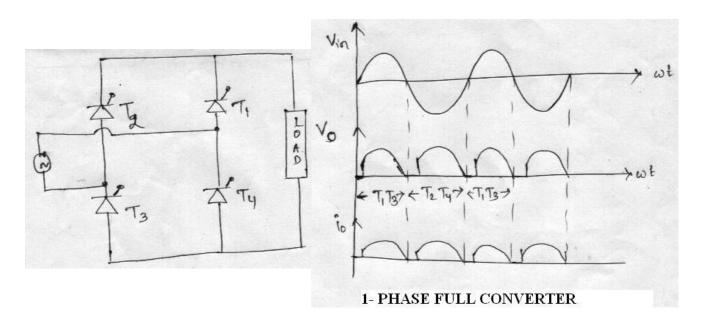

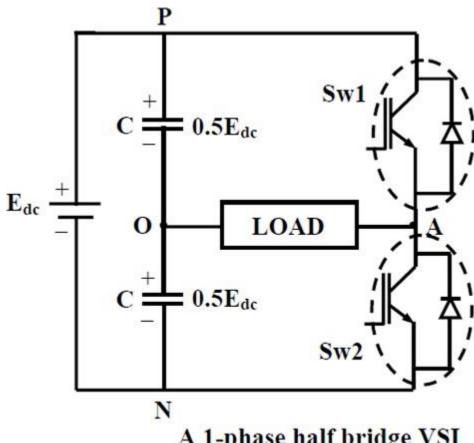

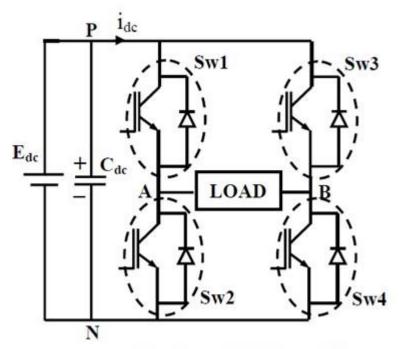

# 3.6 Single phase fully controlled bridge converter with Resistive load only (with & without FD)

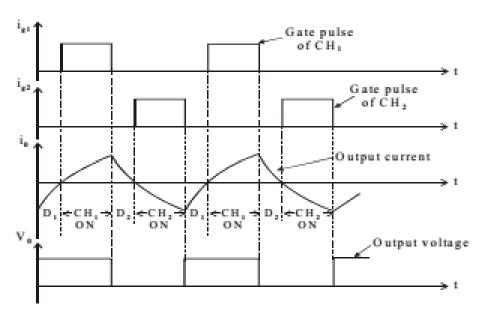

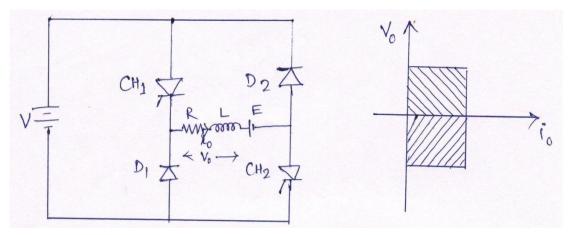

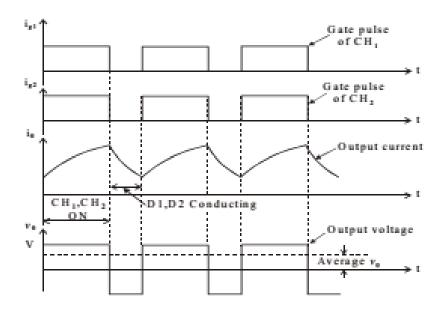

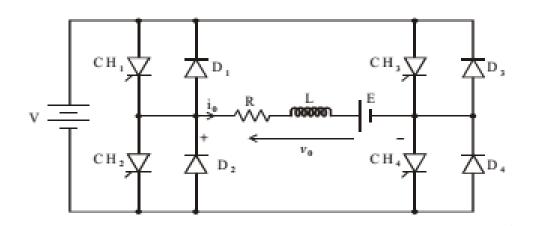

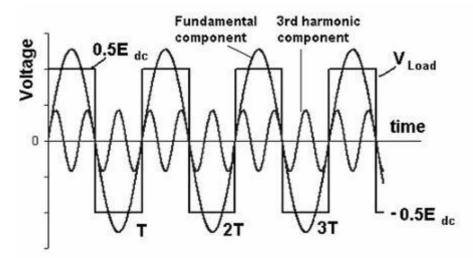

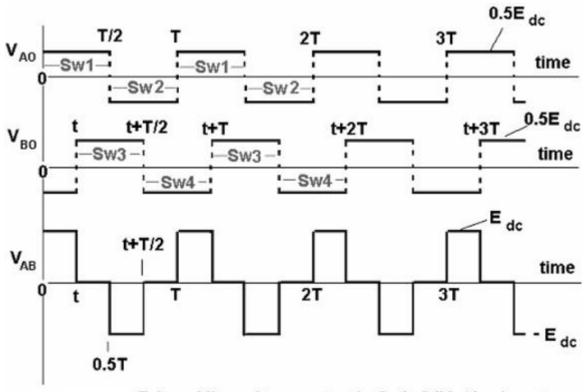

The figure shows the circuit diagram of a single phase fully controlled bridge converter. It is one of the most popular converter circuits and is widely used in the speed control of separately excited dc machines.

The single phase fully controlled bridge converter is obtained by replacing all the diode of the corresponding uncontrolled converter by thyristors. Thyristors T1 and T2 are fired together while T3 and T4 are fired 180° after T1 and T2. From the circuit diagram of Fig 10.3(a) it is clear that for any load current to flow at least one thyristor from the top group (T1, T3) and one thyristor from the bottom group (T2, T4) must conduct and neither T1T3 nor T2T4 can conduct simultaneously. Whenever T3 and T4 are in the forward blocking state and a gate pulse is applied to them, they turn ON and at the same time a negative voltage is applied across T1 and T2 commutating them immediately. Similar is the case for T1 and T2.

The only possible conduction modes when the current i<sub>0</sub> can flow are T1T2 and T3T4. It may happen that at a given moment none of the thyristors conduct. This situation will typically occur when the load current becomes zero in between the firings of T1T2 and T3T4. Once the load current becomes zero all thyristors remain off.

In this mode the load current remains zero. Consequently the converter is said to be operating in the discontinuous conduction mode. Figure shows the voltage across different devices and the dc output voltage during each of these conduction modes. It is to be noted that whenever T1 and T2 conducts, the voltage across T3 and T4 becomes  $-v_i$ . Therefore T3 and T4 can be fired only when  $v_i$  is negative i.e, over the negative half cycle of the input supply voltage. Similarly T1 and T2 can be fired only over the positive half cycle of the input supply. The voltage across the devices when none of the thyristors conduct depends on the off state impedance of each device.

Under normal operating condition of the converter the load current may or may not remain zero over some interval of the input voltage cycle. If  $i_0$  is always greater than zero then the converter is said to be operating in the continuous conduction mode. In this mode of operation of the converter T1T2 and T3T4 conducts for alternate half cycle of the input supply.

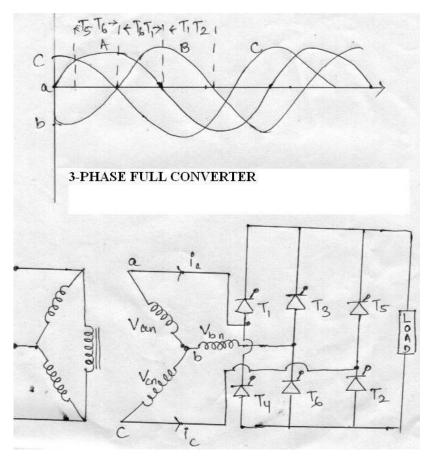

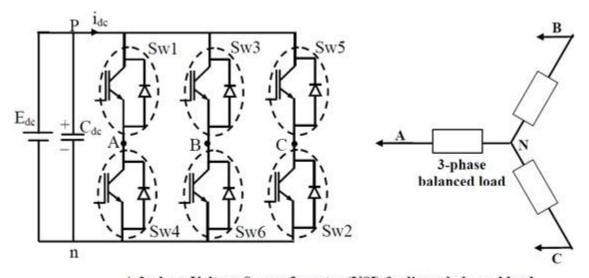

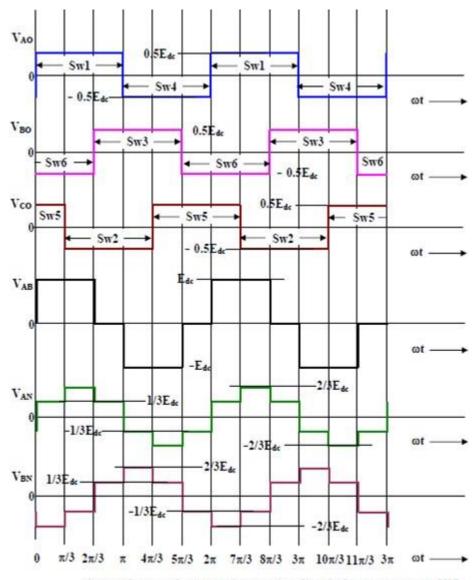

3.7 Explain with circuit diagram and waveforms the operation of fully controlled three phase bridge converter with Restive load (with & with out FD)

#### 3Ф full Converter using Bridge Circuit

$3\Phi$  phase power supply are connected in two ways.

- (1) Star connection

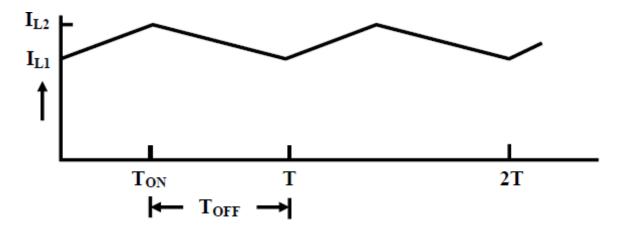

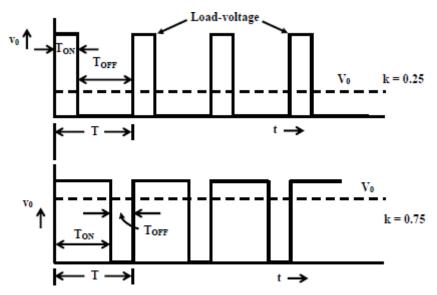

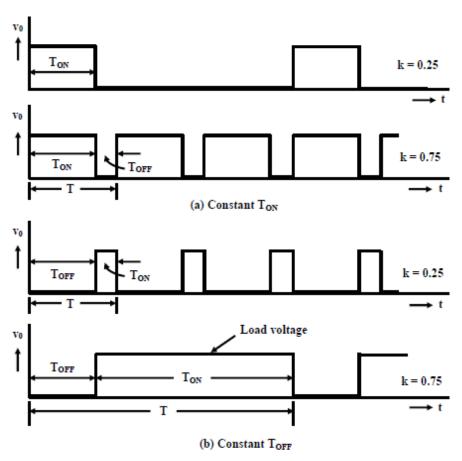

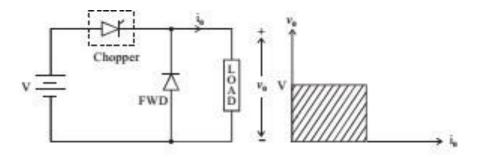

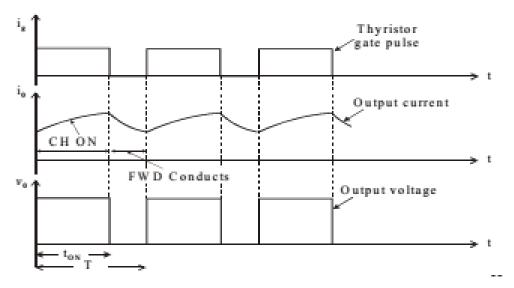

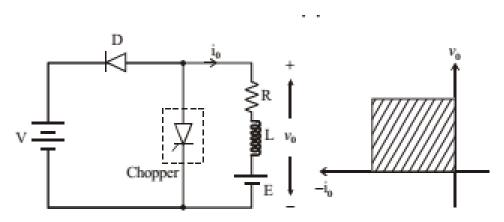

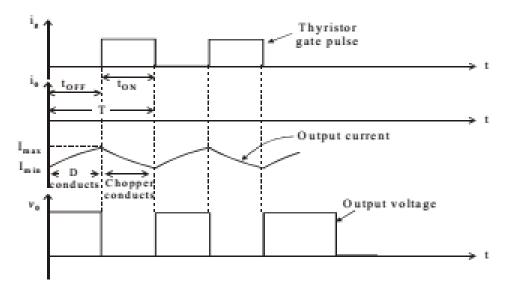

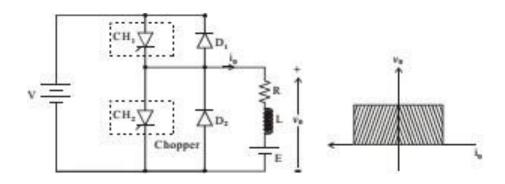

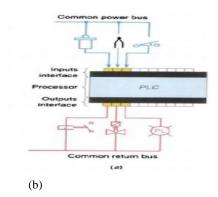

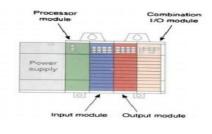

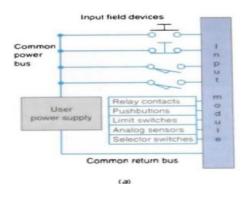

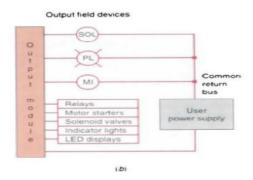

- (2) Delta connection