# **LECTURENOTES**

ON

TH-2 DIGITAL ELECTRONICS AND MICROPROCESSOR

PREPARED BY- RAJEEV RANJAN SETH, Sr. LECTURER, E&TC

For

$5^{TH}$  SEMESTER ELECTRICAL AND ELECTRONICS SENGG.

#### **Unit-1: Basics of Digital Electronics**

Number System-Binary, Octal, Decimal, Hexadecimal - Conversion from one system to another number system.

In digital electronics, the number system is used for representing the information.

The four most common number system are:

- 1. Decimal number system (Base- 10)

- 2. Binary number system (Base- 2)

- 3. Octal number system (Base-8)

- 4. Hexadecimal number system (Base- 16)

The Base or Radix of the number system is the total number of digit used in the number system.

For example, in decimal number system, it represents digit from 0-9 then the base of the system is 10.

#### Important terms:

Bit: A bit is the smallest unit of information. Bits in computer are grouped to form a lager unit of information

Byte: A byte is a combination of eight bits. Eight bits represent a character and is called a byte.

**Nibble:** A nibble is a combination of four bits, in other words a nibble is half a byte.

Word: a word is a combination of 16 bits, 32 bits or 64 bits depending on the computer. 16 is known as quad word.

Kilobyte (kb): A kilobyte has a memory unit of 1024 (2<sup>10</sup>)

Megabyte: a megabyte has a memory unit if 1,048,576 (2<sup>20</sup>). This is approximately 1 million bytes.

Gigabytes (Gb): A gigabyte has a memory unit of 1,073,741,824 (2\*\*30). This approximately billion bytes.

**Terabytes:** a terabyte has a memory unit of (2\*\*40). This is approximately 1 trillion bytes.

#### Note:

```

1024 byte = 1 kilobyte (1kb)

1024 kilobytes = 1 megabytes (1mb)

```

1024 megabyte = 1 gigabytes (1 Gb) 1024 gigabytes =1 terabyte (1tb)

#### 1. Decimal Number System

Decimal number system has base 10 as it uses 10 digits from 0 to 9. In decimal number system, the successive positions to the left of the decimal point represent units, tens, hundreds, thousands, and so on.

Each position represents a specific power of the base (10). For example, the decimal number 1234 consists of the digit 4 in the units position, 3 in the tens position, 2 in the hundreds position, and 1 in the thousands position. Its value can be written as

```

(1 \times 1000 + (2 \times 100 + (3 \times 10 + (4 \times 1)))

(1 \times 10^3 + (2 \times 10^2 + (3 \times 10^1 + (4 \times 10^0)))

1000 + 200 + 30 + 4

1234

```

#### **Binary Number System**

Characteristics of the binary number system are as follows -

- Uses two digits, 0 and 1

- Also called as base 2 number system

- First position in a binary number represents a **0** power of the base (2). Example 2<sup>0</sup>

- Last position in a binary number represents a **x** power of the base (2). Example 2<sup>x</sup> where **x** represents the last position-1

#### Example

Binary Number: 101012

#### **Octal Number System**

Characteristics of the octal number system are as follows -

- Uses eight digits, 0,1,2,3,4,5,6,7

- Also called as base 8 number system

- First position in an octal number represents a **0** power of the base (8). Example 8<sup>0</sup>

- Last position in an octal number represents a **x** power of the base (8). Example 8<sup>x</sup> where **x** represents the last position 1

### **Example**

Octal Number: 12570<sub>8</sub>

### **Hexadecimal Number System**

Characteristics of hexadecimal number system are as follows -

- Uses 10 digits and 6 letters, 0, 1, 2, 3, 4, 5, 6, 7, 8, 9, A, B, C, D, E, F

- Letters represent the numbers starting from 10. A = 10. B = 11, C = 12, D = 13, E = 14, F = 15

- Also called as base 16 number system

- First position in a hexadecimal number represents a **0** power of the base (16). Example, 16<sup>0</sup>

- Last position in a hexadecimal number represents a **x** power of the base (16). Example 16<sup>x</sup> where **x** represents the last position 1

#### Example

Hexadecimal Number: 19FDE<sub>16</sub>

### **Conversion of Number System**

#### **Binary to Decimal**

| Step   | Binary Number | Decimal Number                                                                              |

|--------|---------------|---------------------------------------------------------------------------------------------|

| Step 1 | 101012        | $((1 \times 2^4) + (0 \times 2^3) + (1 \times 2^2) + (0 \times 2^1) + (1 \times 2^0))_{10}$ |

| Step 2 | 101012        | (16 + 0 + 4 + 0 + 1) <sub>10</sub>                                                          |

| Step 3 | 101012        | 21 <sub>10</sub>                                                                            |

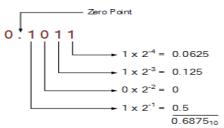

### Example 1

### Example 2

$$1101.0111 = (1 \times 2^{3}) + (1 \times 2^{2}) + (0 \times 2^{1}) + (1 \times 2^{0}) + (0 \times 2^{-1}) + (1 \times 2^{-2}) + (1 \times 2^{-3}) + (1 \times 2^{-4})$$

$$= 8 + 4 + 0 + 1 + 0 + 1/4 + 1/8 + 1/16$$

$$= 8 + 4 + 0 + 1 + 0 + 0.25 + 0.125 + 0.0625 = 13.4375_{10}$$

Hence the decimal equivalent number of  $1101.0111_2$  is given as:  $13.4375_{10}$

### **Octal to Decimal**

| Step   | Octal Number       | Decimal Number                                                                              |

|--------|--------------------|---------------------------------------------------------------------------------------------|

| Step 1 | 12570 <sub>8</sub> | $((1 \times 8^4) + (2 \times 8^3) + (5 \times 8^2) + (7 \times 8^1) + (0 \times 8^0))_{10}$ |

| Step 2 | 12570 <sub>8</sub> | (4096 + 1024 + 320 + 56 + 0) <sub>10</sub>                                                  |

| Step 3 | 125708             | 5496 <sub>10</sub>                                                                          |

# Example 1

### **Hexadecimal to Decimal**

| Step   | Binary<br>Number    | Decimal Number                                                                                      |

|--------|---------------------|-----------------------------------------------------------------------------------------------------|

| Step 1 | 19FDE <sub>16</sub> | $((1 \times 16^4) + (9 \times 16^3) + (F \times 16^2) + (D \times 16^1) + (E \times 16^0))_{10}$    |

| Step 2 | 19FDE <sub>16</sub> | $((1 \times 16^4) + (9 \times 16^3) + (15 \times 16^2) + (13 \times 16^1) + (14 \times 16^0))_{10}$ |

| Step 3 | 19FDE <sub>16</sub> | (65536+ 36864 + 3840 + 208 + 14) <sub>10</sub>                                                      |

| Step 4 | 19FDE <sub>16</sub> | 10646210                                                                                            |

### Example 1

Convert ( E F . B1 ) $_{16}$ = ( ? ) $_{10}$

=  $E \times 16^{1} + F \times 16^{0} + B \times 16^{-1} + 1 \times 16^{-2}$

$= 14 \times 16 + 15 \times 1 + 11 \times (1 / 16) + 1 \times (1 / 256)$

**= 224 + 15 +( 0. 6 8 75) + (0. 0 0 3 9 0 6 2 5)**

= 239 + 0. 6914

= 239.691406

Therefore ( EF.B1)<sub>16</sub> = (2 3 9.6 9 1 4 0 6 )<sub>10</sub>

### **Decimal to Binary**

Decimal numbers can be converted to binary by repeated division of the number by 2 while recording the remainder.

#### Remainder

| 2  | 43 |   | 1   |

|----|----|---|-----|

| 2  | 21 | 1 |     |

| 2  | 10 | 1 |     |

| 2  | 5  | 0 |     |

| 2  | 2  | 1 |     |

| 2  | 1  | 0 |     |

| 53 | 0  | 1 | MSB |

|    |    |   |     |

The remainders are to be read from bottom to top to obtain the binary equivalent.

$$43_{10} = 101011_2$$

$$(458.692)_{10} = (?)_2$$

### **Decimal to Octal**

Decimal numbers can be converted to octal by repeated division of the number by 8 while recording the remainder.

# Remainder

| 8 | 473 |   |

|---|-----|---|

| 8 | 59  | 1 |

| 8 | 7   | 3 |

|   | 0   | 7 |

Reading the remainders from bottom to top,

$$473_{10} = 731_8$$

# Convert (965.198)<sub>10</sub> to (?)<sub>8</sub>

0.198 \* 8 = 1.584 MSB 0.584 \* 8 = 4.672

0.672 \* 8 = 5.376

0.376 \* 8 = 3.008

0.008 \* 8 = 0.064

0.064 \* 8 = 0.512 LSB

# $(0.198)_{10} = (0.145300)_8.$

# **Decimal to Hexadecimal**

Decimal numbers can be converted to octal by repeated division of the number by 16 while recording the remainder.

# Remainder

7 A

Reading the remainders from bottom to top we get,

$$423_{10} = 1A7_{16}$$

( 0.06640625)<sub>10</sub>=( )<sub>16</sub>

| Multiplication | Resultant integer part |

|----------------|------------------------|

|                |                        |

| Multiplication         | Resultant integer part |

|------------------------|------------------------|

| 0.06640625 x 16=1.0625 | 1                      |

| 0.0625 x 16 =1.0       | 1                      |

| 0 x 16=0.0             | 0                      |

$(0.06640625)_{10} = (0.110)_{16}$

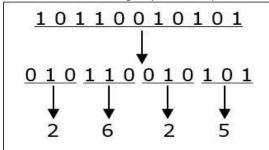

### **Binary to Octal and Vice Versa**

To convert a binary number to octal number, these steps are followed -

- Starting from the least significant bit, make groups of three bits.

- If there are one or two bits less in making the groups, 0s can be added after the most significant bit

- Convert each group into its equivalent octal number

$1011001010_{12} = 2625_8$

To convert an **octal number to binary**, each octal digit is converted to its 3-bit binary equivalent according to this table.

| Octal Digit       | 0   | 1   | 2   | 3   | 4   | 5   | 6   | 7   |

|-------------------|-----|-----|-----|-----|-----|-----|-----|-----|

| Binary Equivalent | 000 | 001 | 010 | 011 | 100 | 101 | 110 | 111 |

$54673_8 = 101100110111011_2$

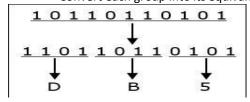

### **Binary to Hexadecimal**

To convert a binary number to hexadecimal number, these steps are followed –

- Starting from the least significant bit, make groups of four bits.

- If there are one or two bits less in making the groups, 0s can be added after the most significant bit.

- Convert each group into its equivalent hexadecimal number.

10110110101<sub>2</sub> = DB5<sub>16</sub>

To convert a **hexadecimal number to binary**, each hexadecimal digit is converted to its 4-bit binary equivalent according to this table.

| Decimal | Hex | Binary |

|---------|-----|--------|

| 0       | 0   | 0000   |

| 1       | 1   | 0001   |

| 2       | 2   | 0010   |

| 3       | 3   | 0011   |

| 4       | 4   | 0100   |

| 5       | 5   | 0101   |

| 6       | 6   | 0110   |

| 7       | 7   | 0111   |

| 8       | 8   | 1000   |

| 9       | 9   | 1001   |

| 10      | А   | 1010   |

| 11      | В   | 1011   |

| 12      | С   | 1100   |

| 13      | D   | 1101   |

| 14      | E   | 1110   |

| 15      | F   | 1111   |

# **Number System Relationship**

The following table depicts the relationship between decimal, binary, octal and hexadecimal number systems.

| HEXADECIMAL | DECIMAL | OCTAL | BINARY |

|-------------|---------|-------|--------|

| 0           | 0       | 0     | 0000   |

| 1           | 1       | 1     | 0001   |

| 2           | 2       | 2     | 0010   |

| 3           | 3       | 3     | 0011   |

| 4           | 4       | 4     | 0100   |

| 5           | 5       | 5     | 0101   |

| 6           | 6       | 6     | 0110   |

| 7           | 7       | 7     | 0111   |

| 8           | 8       | 10    | 1000   |

| 9 | 9  | 11 | 1001 |

|---|----|----|------|

| А | 10 | 12 | 1010 |

| В | 11 | 13 | 1011 |

| С | 12 | 14 | 1100 |

| D | 13 | 15 | 1101 |

| E | 14 | 16 | 1110 |

| F | 15 | 17 | 1111 |

#### Octal to Hexadecimal and vice versa

While converting from octal to hexadecimal, first convert the octal number into binary digit and then further from binary to hexadecimal.

Convert 536 from octal to hexadecimal number

```

(536)_8 = (101) (011) (110)

=(101011110)_2

```

Now forming the group of 4 binary bits to obtain its hexadecimal equivalent,

$(101011110)_2 = (0001) (0101) (1110)$

$=(15E)_{16}$

So the hexadecimal number of 536 is 15E.

While converting from hexadecimal to octal, first convert the hexadecimal number into binary digit and then further from binary to octal.

Convert 15E hexadecimal number to Octal number

$(15E)_{16}$ = (0001) (0101) (1110) = (0001010111110)<sub>2</sub>

Now forming the group of 3 binary bits to obtain its octal equivalent,

$(0001010111110)_2 = (101) (011) (110) = (536)_8$

Arithmetic Operation-Addition, Subtraction, Multiplication, Division, 1's & 2's complement of Binary numbers& Subtraction using complements method

### **ADDITION:**

The four rules of binary addition are:

0 + 0 = 0

0 + 1 = 1

```

1 + 0 = 1

1 + 1 = 0 with a carry-over of 1

Find the sum of the following numbers:

i) 10101 and 11011

Solution:

10101 and 11011

1111 Carry overs

10101

11011

110000

ii) 11001 and 111

Solution:

11001 and 111

1111 Carry overs

11001

111

100000

iii) 10101.101 and 1101.011

Solution:

10101.101 and 1101.011

11 11 11 Carry overs

10101.101

1101.011

100011.000

SUBTRACTION:

The four rules of binary subtraction are:

0 - 0 = 0

1 - 0 = 1

1 - 1 = 0

0 - 1 = 1 with a borrow of 1

Subtract the following numbers:

i) 101 from 1001

Solution:

101 from 1001

1 Borrow

1001

101

100

ii) 111 from 1000

```

Solution:

111 from 1000

# iii) 11010.101 from 101100.011

#### Solution:

11010.101 from 101100.011

1 1 1 Borrow

$101100.011 \\ \underline{11010.101} \\ 10001.110$

# **MULTIPLICATION:**

The rules for multiplication

$0 \times 0 = 0$

$1 \times 0 = 0$

$0 \times 1 = 0$

$1 \times 1 = 1$ (there is no carry or borrow for this)

**Examples of Binary Multiplication**

#### **DIVISION:**

The main rules of the binary division include:

- 1÷1 = 1

- 1÷0 = 0

- 0÷1 = Meaningless

0÷0 = Meaningless

**Evaluate:**

(i) 11001 ÷ 101

Solution:

Hence the quotient is 101

(ii) 11101.01 ÷ 1100

Solution:

Hence the quotient is 10.0111

#### **SIGNED-MAGNITUDE REPRESENTATION**

In this system, a number consists of a magnitude and a symbol which indicates whether the magnitude is positive or negative.

In binary numbers system an extra bit position is used to represent the sign. This extra bit is called the SIGN BIT and is placed before the magnitude of the number to be represented. Generally, the MSB is the sign bit and the convention is that when the sign bit is 0, the number represented is positive and when the sign bit is 1, the number is negative.

$(00000000)_2 = +(0)_{10}$  $(10000000)_2 = -(0)_{10}$

#### 1'S & 2'S COMPLEMENT OF BINARY NUMBERS

The 1's complement of a binary number can be obtained by substituting each 1 by 0 and 0 by 1.

Example:

Binary number-101100

1's complement = 010011

The 2's complement of a binary number is 1 added to the 1's complement of the binary number.

Example:

Binary number=101100

1's complement = 010011

2's complement = 1's complement + 1

=010100

#### SUBTRACTION USING COMPLEMENTS METHOD

1's complement subtraction:

- In 1's complement subtraction, add the 1's complement of subtrahend to minuend.

- If there is carry, then the carry is added to the LSB. This is called end around carry.

- If MSB is 0, the result is Positive.

- If the MSB is 1 then the result is Negative and is in its 1's complement form. Then take its 1's complement to get magnitude in binary.

#### **Evaluate:**

(i) 110101 - 100101

Solution:

1's complement of 10011 is 011010. Hence

Minued - 110101

1's complement of subtrahend - 0 1 1 0 1 0

Carry over - 1 001111

\_\_\_\_1

010000

As MSB is 0, so the number is positive. Henc e the difference is 10000

#### (ii) 101011 - 111001

#### Solution:

1's complement of 111001 is 000110. Hence

Minued - 101011

1's complement - 000110

110001

As MSB is 1, the number is negative. Take 1's complement of 10001

Hence the difference is -01 1 1 0

# (iii) 1011.001 – 110.10

### Solution:

1's complement of 0110.100 is 1001.011 Hence

Minued - 1011.001

1's complement of subtrahend - 1001.011

Carry over - 1 0100.100

$0\,1\,0\,0\,.\,1\,0\,1$

### Hence the required difference is 100.101

### 2's complement subtraction:

- In 2's complement, add 2's complement of subtrahend to the minuend.

- If there is a carry ignore it.

- If the MSB is 0, the result is Positive.

- If the MSB is 1 the result is Negative and is in 2's complement form. Then take its complement to get the magnitude in binary.

# Evaluate:

### 10110 - 11010

#### Solution:

2's complement of 11010 is (00101 + 1) i.e. 00110. Hence

Minued - 10110

2's complement of subtrahend - 00110

Result of addition - 11100

As MSB is 1, the number is negative. Take 2's complement of 11100 So, 1's complement of 11100 is 00011 2's complement is 00011+1=00100 Hence the difference is -100.

#### Digital Code & its application & distinguish between weighted & non-weight Code, Binary codes, excess-3 and Gray codes.

- Digital coding is the process of using binary digits to represent letters, characters and other symbols in a digital format.

- There are several types of digital codes widely used today, but they use the same principle of combining binary numbers to represent a character.

- The most widely used Digital Codes are ASCII(American Standard Code Information Interchange), BCD(Binary Coded Decimal), EBCDIC(Extended Binary Coded Decimal Interchange Code) and Unicode.

Binary codes can be classified into two types.

- Weighted codes

- Unweighted codes

In weighted codes, each digit is assigned a specific weight according to its position.

Examples: 8421code,2421code

The Non - Weighted Code are not positionally weighted. In other words, codes that are not assigned with any weight to each digit position.

Examples: Excess 3 code, Grey code

#### **Excess 3 code**

- Excess-3 code doesn't have any weights. So, it is a non-weighted code.

- We will get the Excess 3 code of a decimal number by adding three to the binary equivalent of that decimal number.

Hence, it is called as Excess 3 code.

- It is a self-complementing code.

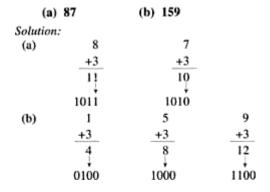

### Convert the following numbers to Excess-3 code

### **Grey Code**

- The Grey code is a non-weighted code.

- No specific weight assigned to the bit positions.

- It exhibits only a single change from one code word to the next sequence.

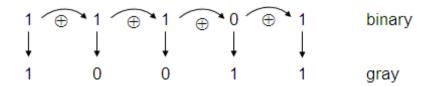

#### Conversion of a Binary number to Gray code

- The first bit(MSB) of the Gray code is the same as the first bit of the binary number

- The second bit of the Gray code equals the exclusive-OR, of the first and second bits of the binary number, i.e. it will be 1 if these binary code bits are different and 0 if they are the same.

- The third Gray code bit equals the exclusive-OR of the second and third bits of the binary number, and so on.

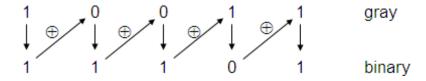

### **Conversion from Gray code to Binary**

- The first binary bit(MSB) is the same as that of the first the Gray code bit.

- The second bit of the binary code equals the exclusive-OR, of the MSB and second bits of the gray code.

- Step 2 is repeated.

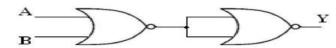

#### **LOGIC GATES:**

- Logic gates are the basic building blocks of any digital system. It is an electronic circuit having one or more than one input and only one output. The relationship between the input and the output is based on certain **logic**.

- In digital system, the basic gates are AND Gate, OR gate, NOT gate.

- NAND and NOR are called universal gates because all the other gates can be derived from it.

- Truth table is the list of all possible combination of input and the corresponding output.

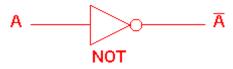

## **NOT** gate

| NOT gate |   |  |

|----------|---|--|

| Α        | Ā |  |

| 0        | 1 |  |

| 1        | 0 |  |

The NOT gate is an electronic circuit that produces an inverted version of the input at its output. It is also known as an *inverter*. If the input variable is A, the inverted output is known as A'.

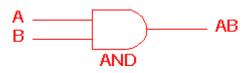

### **AND** gate

| 2 Input AND gate |   |   |  |  |  |  |

|------------------|---|---|--|--|--|--|

| A B A.B          |   |   |  |  |  |  |

| 0                | 0 | 0 |  |  |  |  |

| 0                | 1 | 0 |  |  |  |  |

| 1                | 0 | 0 |  |  |  |  |

| 1                | 1 | 1 |  |  |  |  |

The AND gate is an electronic circuit that gives a **high** output (1) only if **all** its inputs are high. A dot (.) is used to show the AND operation i.e. A.B.

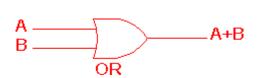

# **OR** gate

| 2 Input OR gate |   |   |  |  |  |  |

|-----------------|---|---|--|--|--|--|

| A B A+B         |   |   |  |  |  |  |

| 0               | 0 | 0 |  |  |  |  |

| 0               | 1 | 1 |  |  |  |  |

| 1               | 0 | 1 |  |  |  |  |

| 1               | 1 | 1 |  |  |  |  |

The OR gate is an electronic circuit that gives a high output (1) if **one or more** of its inputs are high. A plus (+) is used to show the OR operation.

### **NAND** gate

| 2 Input NAND gate |   |   |  |  |  |  |

|-------------------|---|---|--|--|--|--|

| A B A.B           |   |   |  |  |  |  |

| 0                 | 0 | 1 |  |  |  |  |

| 0                 | 1 | 1 |  |  |  |  |

| 1                 | 0 | 1 |  |  |  |  |

| 1                 | 1 | 0 |  |  |  |  |

This is an AND gate followed by a NOT gate. The outputs of all NAND gates are high if any of the inputs are low.

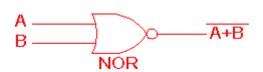

## **NOR** gate

| 2 Input NOR gate   |   |   |  |  |  |  |

|--------------------|---|---|--|--|--|--|

| A B <del>A+B</del> |   |   |  |  |  |  |

| 0                  | 0 | 1 |  |  |  |  |

| 0                  | 1 | 0 |  |  |  |  |

| 1                  | 0 | 0 |  |  |  |  |

| 1                  | 1 | 0 |  |  |  |  |

This is an OR gate followed by a NOT gate. The outputs of all NOR gates are low if **any** of the inputs are high.

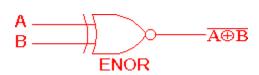

#### **EXOR** gate

| 2 Input EXOR gate |   |   |  |  |  |  |

|-------------------|---|---|--|--|--|--|

| A B A⊕B           |   |   |  |  |  |  |

| 0                 | 0 | 0 |  |  |  |  |

| 0                 | 1 | 1 |  |  |  |  |

| 1                 | 0 | 1 |  |  |  |  |

| 1                 | 1 | 0 |  |  |  |  |

The 'Exclusive-OR' gate is a circuit which will give a high output if either, but not both, of its two inputs are high. An encircled plus sign ( $\oplus$ ) is used to show the EOR operation.

# **EXNOR** gate

| 2 Input EXNOR gate |   |   |  |  |  |  |

|--------------------|---|---|--|--|--|--|

| A B A⊕B            |   |   |  |  |  |  |

| 0                  | 0 | 1 |  |  |  |  |

| 0                  | 1 | 0 |  |  |  |  |

| 1                  | 0 | 0 |  |  |  |  |

| 1                  | 1 | 1 |  |  |  |  |

The 'Exclusive-NOR' gate circuit does the opposite to the EOR gate. It will give a low output if either, but not both, of its two inputs are high. The symbol is an EXOR gate with a small circle on the output. The small circle represents inversion.

| Name | Graphical Symbol      | Algebraic<br>Function          | Truth Table                               |

|------|-----------------------|--------------------------------|-------------------------------------------|

| AND  | A F                   | F = A • B<br>or<br>F = AB      | AB F<br>0000<br>010<br>100<br>111         |

| OR   | A B                   | F = A + B                      | AB F<br>00 0<br>01 1<br>10 1<br>11 1      |

| NOT  | A — F                 | $F = \overline{A}$ or $F = A'$ | A F<br>0 1<br>1 0                         |

| NAND | A F                   | $F = \overline{AB}$            | AB F<br>0011<br>011<br>101<br>110         |

| NOR  | A F                   | $F = \overline{A + B}$         | A B F<br>0 0 1<br>0 1 0<br>1 0 0<br>1 1 0 |

| XOR  | $A \longrightarrow F$ | $F = A \oplus B$               | A B F<br>0 0 0<br>0 1 1<br>1 0 1<br>1 1 0 |

# 1 UNIVERSAL GATES & ITS REALISATION:

NAND and NOR are called **universal gates** because all the other gates can be derived from it.

| LOGIC<br>FUNCTION | SYMBOL                                                                                        | CIRCUIT USING NAND GATES ONLY |

|-------------------|-----------------------------------------------------------------------------------------------|-------------------------------|

| Inverter          | A — — — Ā                                                                                     | A TOO A                       |

| AND               | A B A B                                                                                       | А<br>В О О О О О А · В        |

| OR                | A + B                                                                                         |                               |

| NOR               | $A \longrightarrow \overline{A+B}$                                                            |                               |

| XOR               | $\begin{array}{c} A \\ B \end{array} \longrightarrow \begin{array}{c} A \oplus B \end{array}$ |                               |

| XNOR              | $ \begin{array}{c} A \\ B \end{array} $                                                       |                               |

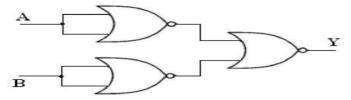

#### II. Implementation using NOR gate:

(a) NOT gate:

$$Y = A'$$

(b) AND gate:

$$Y = A \cdot B$$

(c) OR gate:

$$Y = A + B$$

(d) NAND gate:

$$Y = (AB)'$$

(e) Ex-NOR gate:

$$Y = A \odot B = (A \oplus B)'$$

### **BOOLEAN ALGEBRA, BOOLEAN EXPRESSION, DEMORGAN'S THEOREMS**

- Boolean algebra is the set of rules used to simplify the logic expression without changing its functionality.

- It is used when number of variable is less (1,2,3)

#### **Boolean Theorem:**

#### 1.INVERSION law

This law uses the NOT operation. The inversion law states that double inversion of a variable results in the original variable

$$\frac{=}{A} = A$$

#### 2.AND law

These laws use the AND operation. Therefore, they are called as AND laws.

(i)

$$A.0 = 0$$

(ii)

$$A.1 = A$$

$$(iii)$$

A.A = A

(iii)

$$A.A = A$$

(iv)  $A.\overline{A} = 0$

#### 3. OR law

These laws use the OR operation. Therefore, they are called as **OR** laws.

(i)

$$A + 0 = A$$

(ii)

$$A + 1 = 1$$

(iii)

$$A + A = A$$

(i)

$$A + 0 = A$$

(ii)  $A + 1 = 1$

(iii)  $A + A = A$  (iv)  $A + \overline{A} = 1$

#### 4. Commutative law

(ii)

$$A + B = B + A$$

Commutative law states that changing the sequence of the variables does not have any effect on the output of a logic circuit.

### 5. Associative law

(i)

$$(A.B).C = A.(B.C)$$

(ii)

$$(A + B) + C = A + (B + C)$$

This law states that when ORing/ANDing more than two variables, the result is the same regardless of the grouping of the variables.

### 6. Distributive law

Distributive law states the following condition.

$$A.(B+C) = A.B + A.C$$

This law states that ORing two or more variables and then ANDing the result with a single variable is equivalent to ANDing the single variable with each of the two or more variables and then ORing the product.

$$A+(B.C) = (A+B). (A+C)$$

This law states that ANDing two or more variables and then ORing the result with a single variable is equivalent to ORing the single variable with each of the two or more variables and then ANDing the sum.

### 7. Absorption Laws

Absorption law involves in linking of a pair of binary operations.

i.

$$A+AB=A$$

ii.

$$A(A+B) = A$$

iii.

$$A+\bar{A}B = A+B$$

iv.

$$A.(\bar{A}+B) = AB$$

#### 8. Consensus Laws

i. AB + A'C + BC = AB + A'C

ii. (A+B).(A'+C).(B+C) = (A+B).(A'+C)

#### **DEMORGAN'S THEOREM**

The first theorem states that the complement of a product is equal to the sum of the complements. That is if the variables are A and B, then

$$\overline{A} \overline{B} = \overline{A} + \overline{B}$$

> The second theorem states that, the complement of a sum is equal to the product of the complements. In equation form, this can be written as

$$\overline{A + B} = \overline{A} \overline{B}$$

> Demorgan's Theorem can be proved for any number of variables; proof of these two theorems for two variables can be found in the below truth table

| A | В | Ā | B | A+B | A · B | $\overline{A} + \overline{B}$ | $\overline{A} \cdot \overline{B}$ | A·B | $\bar{A} + \bar{B}$ |

|---|---|---|---|-----|-------|-------------------------------|-----------------------------------|-----|---------------------|

| 0 | 0 | 1 | 1 | 0   | 0     | 1                             | 1                                 | 1   | 1                   |

| 0 | 1 | 1 | 1 | 1   | 0     | 0                             | 0                                 | 1   | 1                   |

| 1 | 0 | 0 | 0 | 1   | 0     | 0                             | 0                                 | 1   | 1                   |

| 1 | 1 | 0 | 0 | 1   | 1     | 0                             | 0                                 | 0   | 0                   |

A study of truth table makes clear that columns 7 and 8 are equal. Therefore,

$$\overline{A + B} = \overline{A} \overline{B}$$

Similarly, columns 9 and 10 are equal. Therefore,

$$\overline{A} \overline{B} = \overline{A} + \overline{B}$$

# **REPRESENT LOGIC EXPRESSION: SOP & POS FORMSSum Of Product (SOP)**

- Sum of Product is the abbreviated form of SOP. Sum of product form is a form of expression in Boolean algebra in which different product terms of inputs are being summed together.

- This product is not arithmetical multiply but it is Boolean logical AND and the Sum is Boolean logical OR.

- Example:

- In SOP form, each product term is known as minterms

- The product of all literals, either with complement or without complement, is known as **minterm**. The min terms for two variable x and y are x'y', x'y, xy' and xy.

- If the variable value is 1, we will take the variable without its complement.

If the variable value is 0, take its complement.

■ The minterms can be represented by m<sub>0</sub>, m<sub>1</sub>, m<sub>2</sub>, m<sub>3</sub>......; the suffix indicates the decimal code corresponding to the minterm combination.

#### Types of Sum of Product (SOP) Forms

There are few different forms of Sum of Product.

- Canonical SOP Form

- Non-Canonical SOP Form

- Minimal SOP Form

#### **Canonical SOP Form**

- Canonical SOP form means Canonical Sum of Products form. In this form, each product term contains all literals. So, these product terms are nothing but the min terms. Hence, canonical SOP form is also called as sum of min terms form.

- The expression of the canonical SOP is denoted with sign summation ( $\Sigma$ ), and the minterms in the bracket are taken when the output is true.

- The Boolean function of output is, f = p'qr + pq'r + pqr' + pqr. This is the canonical SOP form of output, f. We can also represent this function in following two notations. f=m3+m5+m6+m7 f=Σm(3,5,6,7)

#### Product of Sum(POS)

- Product of Sum is the abbreviated for POS. The product of Sum form is a form in which products of different sum terms of inputs are taken.

- These are not arithmetic product and sum but they are logical Boolean AND and OR respectively.

- Example:

- In POS form, each sum term is known as maxterms.

- The sum of all literals, either with complement or without complement, is known as **maxterm**. The maxterms for two variable x and y are x'+y', x'+y, x+y' and x+y.

- If the variable value is 0, we will take the variable without its complement.

If the variable value is 1, take its complement.

- The maxterms can be represented by M<sub>0</sub>, M<sub>1</sub>, M<sub>2</sub>, M<sub>3</sub>......; the suffix indicates the decimal code corresponding to the maxterm combination.

- Types of Sum Of Product (SOP) Forms

There are few different forms of Sum of Product.

- Canonical SOP Form

- Non-Canonical SOP Form

- Minimal SOP Form

#### **Canonical POS Form**

- Canonical POS form means Canonical Product of Sums form. In this form, each sum term contains all literals. So, these sum terms are nothing but the Max terms. Hence, canonical POS form is also called as product of Maxterms form.

- lacktriangle The expression this is denoted by  $\Pi$  and the max terms in the bracket are taken when the output is false.

- The Boolean function of output is, f = p+q+r. p+q+r'. p+q'+r. This is the canonical POS form of output, f. We can also represent this function in following two notations.

$f=M_0.M_1.M_2.M_4$  $f=\prod M(0,1,2,4)$

### Two variable minterms and maxterms.

| X | у | Index | Minterm                                                      | Maxterm                                             |

|---|---|-------|--------------------------------------------------------------|-----------------------------------------------------|

| 0 | 0 | 0     | $\mathbf{m}_0 = \overline{\mathbf{x}} \overline{\mathbf{y}}$ | $\mathbf{M_0} = \mathbf{x} + \mathbf{y}$            |

| 0 | 1 | 1     | $\mathbf{m_1} = \overline{\mathbf{x}} \ \mathbf{y}$          | $\mathbf{M_1} = \mathbf{x} + \overline{\mathbf{y}}$ |

| 1 | 0 | 2     | $\mathbf{m_2} = \mathbf{x}  \overline{\mathbf{y}}$           | $\mathbf{M}_2 = \overline{\mathbf{x}} + \mathbf{y}$ |

| 1 | 1 | 3     | $m_3 = x y$                                                  | $M_3 = \overline{x} + \overline{y}$                 |

#### Three variable minterms and maxterms

|   | Variables |   | Min terms      | Max terms                 |

|---|-----------|---|----------------|---------------------------|

| A | В         | С | m <sub>i</sub> | $\mathbf{M}_{\mathrm{i}}$ |

| 0 | 0         | 0 | A' B' C' = m 0 | A + B + C = M 0           |

| 0 | 0         | 1 | A' B' C = m 1  | A + B + C' = M 1          |

| 0 | 1         | 0 | A' B C' = m 2  | A + B' + C = M 2          |

| 0 | 1         | 1 | A' B C = m 3   | A + B' + C' = M 3         |

| 1 | 0         | 0 | A B' C' = m 4  | A' + B + C = M 4          |

| 1 | 0         | 1 | A B' C = m 5   | A' + B + C' = M 5         |

| 1 | 1         | 0 | A B C' = m 6   | A' + B' + C = M 6         |

| 1 | 1         | 1 | A B C = m 7    | A' + B' + C' = M 7        |

#### Conversion of SOP form to standard SOP form or Canonical SOP form

For getting the standard SOP form of the given non-standard SOP form, we will add all the variables in each product term which do not have all the variables. By using the Boolean algebraic law, (x + x' = 1) and by following the below steps we can easily convert the normal SOP function into standard SOP form.

- o Multiply each non-standard product term by the sum of its missing variable and its complement.

- o Repeat step 1, until all resulting product terms contain all variables

- For each missing variable in the function, the number of product terms doubles.

## Example:

Convert the non standard SOP function F = AB + A C + B C

Sol:

F = AB + AC + BC

= A B (C + C') + A (B + B') C + (A + A') B C

= A B C + A B C' + A B C + A B' C + A B C + A' B C

= A B C + A B C' + A B' C + A' B C

So, the standard SOP form of non-standard form is F = A B C + A B C' + A B' C + A' B C

#### Conversion of POS form to standard POS form or Canonical POS form

For getting the standard POS form of the given non-standard POS form, we will add all the variables in each product term that do not have all the variables. By using the Boolean algebraic law (x \* x' = 0) and by following the below steps, we can easily convert the normal POS function into a standard POS form.

- By adding each non-standard sum term to the product of its missing variable and its complement, which results in 2 sum terms

- O Applying Boolean algebraic law, x + y z = (x + y) \* (x + z)

- By repeating step 1, until all resulting sum terms contain all variables

By these three steps, we can convert the POS function into a standard POS function.

### **Example:**

$$F = (p' + q + r) * (q' + r + s') * (p + q' + r' + s)$$

1. Term (p' + q + r)

As we can see that the variable s or s' is missing in this term. So we add s\*s' = 0 in this term.

$$(p'+q+r+s*s') = (p'+q+r+s)*(p'+q+r+s')$$

### 2. Term (q' + r + s')

Similarly, we add p\*p' = 1 in this term for getting the term containing all the variables.

$$(q'+r+s'+p*p') = (p+q'+r+s')*(p'+q'+r+s')$$

#### 3. Term (q' + r + s')

Now, there is no need to add anything because all the variables are contained in this term.

So, the standard POS form equation of the function is

$$F = (p' + q + r + s)*(p' + q + r + s')*(p + q' + r + s')*(p' + q' + r + s')*(p + q' + r' + s)$$

#### Conversion of SOP form to POS form

For getting the POS form of the given SOP form expression, we will change the symbol  $\prod$  to  $\sum$ . After that, we will write the numeric indexes of the variables which are missing in the boolean function.

There are the following steps used to convert the SOP function  $F = \sum x$ , y, z (0, 2, 3, 5, 7) = x' y' z' + z y' z' + x y' z + xyz' + xyz into POS:

- In the first step, we change the operational sign to  $\prod$ .

- We find the missing indexes of the terms, 001, 110, and 100.

- We write the sum form of the noted terms.

$$001 = (x + y + z)$$

$$100 = (x + y' + z')$$

$$110 = (x + y' + z')$$

So, the POS form is:

$$F = \Pi x, y, z (1, 4, 6) = (x + y + z) * (x + y' + z') * (x + y' + z')$$

## Conversion of POS to SOP form

For getting the SOP form from the POS form, we have to change the symbol  $\prod$  to  $\Sigma$ . After that, we write the numeric indexes of missing variables of the given Boolean function.

There are the following steps to convert the POS function  $F = \Pi x$ , y, z(2, 3, 5) = x y' z' + x y' z + x y z' into SOP form:

- 1. In the first step, we change the operational sign to  $\Sigma$ .

- 2. Next, we find the missing indexes of the terms, 000, 110, 001, 100, and 111.

- 3. Finally, we write the product form of the noted terms.

$$000 = x' * y' * z'$$

$$001 = x' * y' * z$$

$$100 = x * y' * z'$$

$$110 = x * y* z'$$

$$111 = x * y * z$$

So the SOP form is:

$$F = \Sigma x, y, z (0, 1, 4, 6, 7) = (x' * y' * z') + (x' * y' * z) + (x * y' * z') + (x * y * z') + (x * y * z')$$

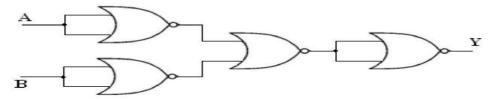

#### Karnaugh map

- Karnaugh map or K-Map method is most suitable for minimizing Boolean functions. With the help of the K-map method, we can find the simplest POS and SOP expression, which is known as the minimum expression.

- It is a graphical method, which consists of 2<sup>n</sup> cells for 'n' variables. The adjacent cells are differed only in single bit position.

- Just like the truth table, a K-map contains all the possible values of input variables and their corresponding output values.

- The K-map method is used for expressions containing 2, 3, 4, and 5 variables.

- The K-map grid is filled using 0's and 1's. The K-map is solved by making groups.

### These are the following steps used to solve the expressions using K-map:

- 1. First, we find the K-map as per the number of variables.

- 2. Find the maxterm and minterm in the given expression.

- 3. Fill cells of K-map for SOP with 1 respective to the minterm.

- 4. Fill cells of the block for POS with 0 respective to the maxterm.

- 5. Next, we create rectangular groups that contain total terms in the power of two like 2, 4, 8, ... and try to cover as many elements as we can in one group.

- 6. With the help of these groups, we find the product terms and sum them up for the SOP form.

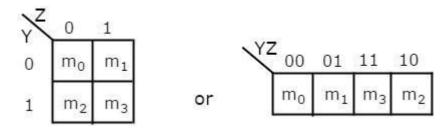

#### 2 Variable K-Map

The number of cells in 2 variable K-map is four, since the number of variables is two. The following figure shows **2 variable K-Map**.

- There is only one possibility of grouping 4 adjacent min terms.

- The possible combinations of grouping 2 adjacent min terms are {(m<sub>0</sub>, m<sub>1</sub>), (m<sub>2</sub>, m<sub>3</sub>), (m<sub>0</sub>, m<sub>2</sub>) and (m<sub>1</sub>, m<sub>3</sub>)}.

### 3 Variable K-Map

The number of cells in 3 variable K-map is eight, since the number of variables is three. The following figure shows **3 variable K-Map**.

| XX | 00             | 01             | 11             | 10             |

|----|----------------|----------------|----------------|----------------|

| 0  | m <sub>0</sub> | $m_1$          | m <sub>3</sub> | m <sub>2</sub> |

| 1  | m <sub>4</sub> | m <sub>5</sub> | m <sub>7</sub> | m <sub>6</sub> |

- There is only one possibility of grouping 8 adjacent min terms.

- The possible combinations of grouping 4 adjacent min terms are  $\{(m_0, m_1, m_3, m_2), (m_4, m_5, m_7, m_6), (m_0, m_1, m_4, m_5), (m_1, m_3, m_5, m_7), (m_3, m_2, m_7, m_6) \text{ and } (m_2, m_0, m_6, m_4)\}.$

- The possible combinations of grouping 2 adjacent min terms are  $\{(m_0, m_1), (m_1, m_3), (m_3, m_2), (m_2, m_0), (m_4, m_5), (m_5, m_7), (m_7, m_6), (m_6, m_4), (m_0, m_4), (m_1, m_5), (m_3, m_7) \text{ and } (m_2, m_6)\}.$

- If x=0, then 3 variable K-map becomes 2 variable K-map.

### 4 Variable K-Map

The number of cells in 4 variable K-map is sixteen, since the number of variables is four. The following figure shows **4 variable K-Map**.

| WX YZ | 00              | 01              | 11              | 10              |

|-------|-----------------|-----------------|-----------------|-----------------|

| 00    | m <sub>0</sub>  | m <sub>1</sub>  |                 |                 |

| 01    | m <sub>4</sub>  | m <sub>5</sub>  | m <sub>7</sub>  | m <sub>6</sub>  |

| 11    | m <sub>12</sub> | m <sub>13</sub> | m <sub>15</sub> | m <sub>14</sub> |

| 10    | m <sub>8</sub>  | m <sub>9</sub>  | m <sub>11</sub> | m <sub>10</sub> |

- There is only one possibility of grouping 16 adjacent minterm.

- Let R<sub>1</sub>, R<sub>2</sub>, R<sub>3</sub> and R<sub>4</sub> represents the min terms of first row, second row, third row and fourth row respectively. Similarly, C<sub>1</sub>, C<sub>2</sub>, C<sub>3</sub> and C<sub>4</sub> represents the min terms of first column, second column, third column and fourth column respectively. The possible combinations of grouping 8 adjacent min terms are {(R<sub>1</sub>, R<sub>2</sub>), (R<sub>2</sub>, R<sub>3</sub>), (R<sub>3</sub>, R<sub>4</sub>), (R<sub>4</sub>, R<sub>1</sub>), (C<sub>1</sub>, C<sub>2</sub>), (C<sub>2</sub>, C<sub>3</sub>), (C<sub>3</sub>, C<sub>4</sub>), (C<sub>4</sub>, C<sub>1</sub>)}.

- If w=0, then 4 variable K-map becomes 3 variable K-map.

#### **Don't Care condition**

- The "Don't Care" conditions allow us to replace the empty cell of a <a href="K-Map">K-Map</a> to form a grouping of the variables. While forming groups of cells, we can consider a "Don't Care" cell as either 1 or 0 or we can simply ignore that cell. Therefore, "Don't Care" condition can help us to form a larger group of cells.

- A Don't Care cell can be represented by a cross(X) or (d) in K-Maps representing a invalid combination.

# **UNIT-2**

### **COMBINATIONAL LOGIC CIRCUITS**

- > The combinational logic circuits are the circuits that contain different types of logic gates.

- The output of the combinational circuit is determined from the present combination of inputs, regardless of the previous input.

- The input variables, logic gates, and output variables are the basic components of the combinational logic circuit.

- > There are different types of combinational logic circuits, such as Adder, Subtractor, Decoder, Encoder, Multiplexer, and De-multiplexer.

Design procedure of Combinational circuits

- Find the required number of input variables and outputs from given specifications.

- Formulate the Truth table. If there are 'n' input variables, then there will be 2n possible combinations. For each combination of input, find the output values.

- Find the Boolean expressions for each output. If necessary, simplify those expressions.

- Implement the above Boolean expressions corresponding to each output by using Logic gates.

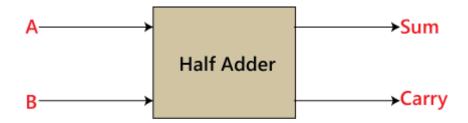

#### **ADDER:**

Adder circuit is a combinational digital circuit that is used for adding two numbers. A typical adder circuit produces a sum bit (denoted by S) and a carry bit (denoted by C) as the output.

Adder circuits are of two types: Half adder and Full adder

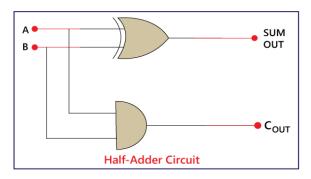

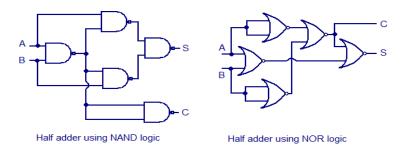

#### **HALF ADDER:**

Half adder is a combinational arithmetic circuit that adds two single bit numbers and produces a sum and carry as the output.

There are two inputs named as A and B and the outputs are named as Sum (S) and Carry (C).

Truth Table

| Inp | uts | Out | puts  |

|-----|-----|-----|-------|

| Α   | В   | Sum | Carry |

| 0   | 0   | 0   | 0     |

| 0   | 1   | 1   | 0     |

| 1   | 0   | 1   | 0     |

| 1   | 1   | 0   | 1     |

From Truth table, the Boolean functions for each output as

$S=A \bigoplus B$

C=AB

The logical diagram of Half adder is shown in the following figure.

NAND gates or NOR gates can be used for realizing the half adder in universal logic and the relevant circuit diagrams are shown in the figure below.

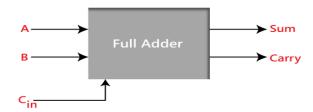

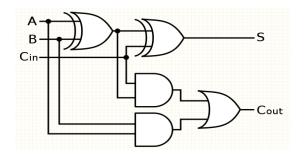

### **FULL ADDER**

Full Adder is the adder which adds three single bit inputs and produces two outputs. The first two inputs are A and B and the third input is an input carry as C<sub>in</sub>. The output carry is designated as Carry and the normal output is designated as S which is SUM.

# **Block diagram**

### **Truth Table**

|   | Inputs |                 | Out | puts  |

|---|--------|-----------------|-----|-------|

| Α | В      | C <sub>in</sub> | Sum | Carry |

| 0 | 0      | 0               | 0   | 0     |

| 0 | 0      | 1               | 1   | 0     |

| 0 | 1      | 0               | 1   | 0     |

| 0 | 1      | 1               | 0   | 1     |

| 1 | 0      | 0               | 1   | 0     |

| 1 | 0      | 1               | 0   | 1     |

| 1 | 1      | 0               | 0   | 1     |

| 1 | 1      | 1               | 1   | 1     |

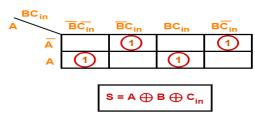

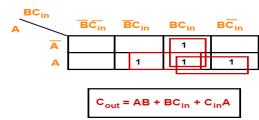

### K-map for SUM and CARRY

# For C<sub>in</sub>:

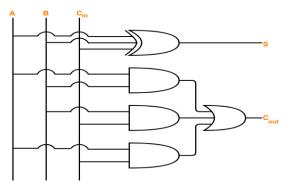

# **Logical Diagram:**

Full Adder Logic Diagram

OR

$SUM = A \oplus B \oplus C_{inn}$

And

**CARRY**

$$\begin{split} &C_o = \overline{A}BC_i + A\overline{B}C_i + AB\overline{C}_i + ABC_i \\ &= C_i(\overline{A}B + A\overline{B}) + AB(\overline{C}_i + C_i) \\ &= C_i(A \oplus B) + AB \end{split}$$

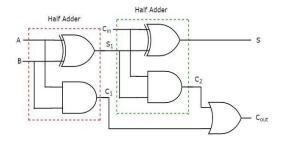

# Full Addrer Using Half adder

### **HALF SUBTRACTOR**

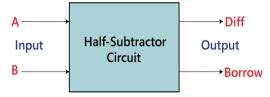

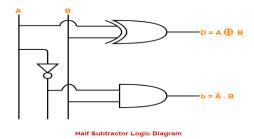

The half subtractor is a combinational circuit. It has two inputs and two outputs. This circuit is used to subtract two single bit binary numbers A and B. The 'difference' and 'borrow' are two output states of the half subtractor.

# Block diagram

#### **Truth Table**

| Inp | uts | Out  | puts   |

|-----|-----|------|--------|

| Α   | В   | Diff | Borrow |

| 0   | 0   | 0    | 0      |

| 0   | 1   | 1    | 1      |

| 1   | 0   | 1    | 0      |

| 1   | 1   | 0    | 0      |

The SOP form of the **Diff** and **Borrow** is as follows:

Diff= A'B+AB' Borrow = A'B

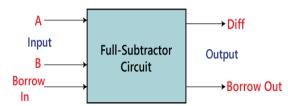

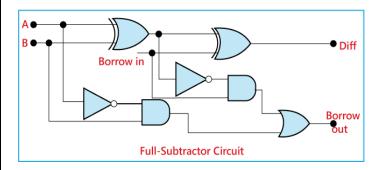

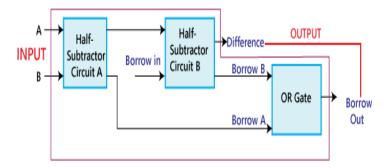

#### **FULL SUBTRACTOR**

The full subtractor is used to subtract three 1-bit numbers A, B, and C, which are minuend, subtrahend, and borrow, respectively. The full subtractor has three input states and two output states i.e., diff and borrow.

# Block diagram

### **Truth Table**

|   | Inputs |          | Out  | puts   |

|---|--------|----------|------|--------|

| Α | В      | Borrowin | Diff | Borrow |

| 0 | 0      | 0        | 0    | 0      |

| 0 | 0      | 1        | 1    | 1      |

| 0 | 1      | 0        | 1    | 1      |

| 0 | 1      | 1        | 0    | 1      |

| 1 | 0      | 0        | 1    | 0      |

| 1 | 0      | 1        | 0    | 0      |

| 1 | 1      | 0        | 0    | 0      |

| 1 | 1      | 1        | 1    | 1      |

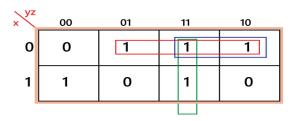

The SOP form can be obtained with the help of K-map as:

| x yz | 00 | 01 | 11 | 10 |

|------|----|----|----|----|

| 0    | 0  | 1  | 0  | 1  |

| 1    | 1  | 0  | 1  | 0  |

Diff=xy' z'+x' y' z+xyz+x'yz'

Borrow=x' z+x' y+yz

The full subtractor logic circuit diagram

Construction of Full Subtractor Circuit using half subtractor:

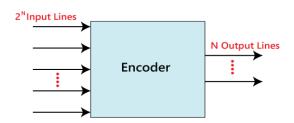

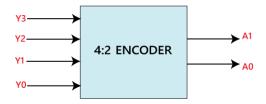

### **ENCODERS**

The combinational circuits that change the binary information into N output lines are known as **Encoders**. The binary information is passed in the form of  $2^N$  input lines. The output lines define the N-bit code for the binary information. At a time, only one input line is activated for simplicity.

There are various types of encoders which are as follows:

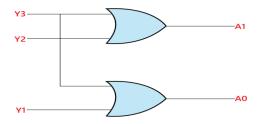

# 4 to 2 line Encoder:

In 4 to 2 line encoder, there are total of four inputs, i.e.,  $Y_0$ ,  $Y_1$ ,  $Y_2$ , and  $Y_3$ , and two outputs, i.e.,  $A_0$  and  $A_1$ . In 4-input lines, one input-line is set to true at a time to get the respective binary code in the output side.

# Block Diagram:

### **Truth Table:**

|                | INF            | PUTS           |                | OUTI           | PUTS           |

|----------------|----------------|----------------|----------------|----------------|----------------|

| Υ <sub>3</sub> | Y <sub>2</sub> | Y <sub>1</sub> | Y <sub>0</sub> | A <sub>1</sub> | A <sub>0</sub> |

| 1              | 0              | 0              | 0              | 0              | 0              |

| 0              | 1              | 0              | 0              | 0              | 1              |

| 0              | 0              | 1              | 0              | 1              | 0              |

| 0              | 0              | 0              | 1              | 1              | 1              |

The logical expression of the term A0 and A1 is as follows:

$A_1 = Y_3 + Y_2$  $A_0 = Y_3 + Y_1$

Logical circuit of the above expressions is given below:

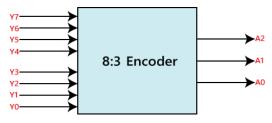

#### 8 to 3 line Encoder:

The 8 to 3 line Encoder is also known as **Octal to Binary Encoder**. In 8 to 3 line encoder, there is a total of eight inputs, i.e.,  $Y_0$ ,  $Y_1$ ,  $Y_2$ ,  $Y_3$ ,  $Y_4$ ,  $Y_5$ ,  $Y_6$ , and  $Y_7$  and three outputs, i.e.,  $A_0$ ,  $A_1$ , and  $A_2$ . In 8-input lines, one input-line is set to true at a time to get the respective binary code in the output side.

# Block Diagram:

#### Truth Table:

|                       |                |                       | INP            | UTS                   |                |                |                |                | OUTPUT         | S              |

|-----------------------|----------------|-----------------------|----------------|-----------------------|----------------|----------------|----------------|----------------|----------------|----------------|

| <b>Y</b> <sub>7</sub> | Y <sub>6</sub> | <b>Y</b> <sub>5</sub> | Y <sub>4</sub> | <b>Y</b> <sub>3</sub> | Y <sub>2</sub> | Y <sub>1</sub> | Y <sub>0</sub> | A <sub>2</sub> | A <sub>1</sub> | A <sub>0</sub> |

| 0                     | 0              | 0                     | 0              | 0                     | 0              | 0              | 1              | 0              | 0              | 0              |

| 0                     | 0              | 0                     | 0              | 0                     | 0              | 1              | 0              | 0              | 0              | 1              |

| 0                     | 0              | 0                     | 0              | 0                     | 1              | 0              | 0              | 0              | 1              | 0              |

| 0                     | 0              | 0                     | 0              | 1                     | 0              | 0              | 0              | 0              | 1              | 1              |

| 0                     | 0              | 0                     | 1              | 0                     | 0              | 0              | 0              | 1              | 0              | 0              |

| 0                     | 0              | 1                     | 0              | 0                     | 0              | 0              | 0              | 1              | 0              | 1              |

| 0                     | 1              | 0                     | 0              | 0                     | 0              | 0              | 0              | 1              | 1              | 0              |

| 1                     | 0              | 0                     | 0              | 0                     | 0              | 0              | 0              | 1              | 1              | 1              |

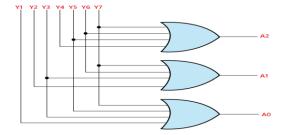

The logical expression of the term A0, A1, and A2 are as follows:

$A_2=Y_4+Y_5+Y_6+Y_7$   $A_1=Y_2+Y_3+Y_6+Y_7$  $A_0=Y_7+Y_5+Y_3+Y_1$

Logical circuit of the above expressions is given below:

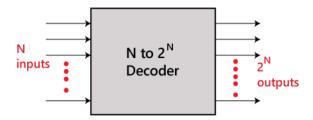

#### **DECODER**

The combinational circuit that change the binary information into  $2^N$  output lines is known as **Decoders.** The binary information is passed in the form of N input lines. The output lines define the  $2^N$ -bit code for the binary information. In simple words, the **Decoder** performs the reverse operation of the **Encoder**. At a time, only one input line is activated for simplicity.

There are various types of decoders which are as follows:

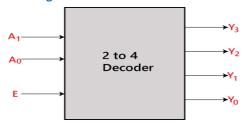

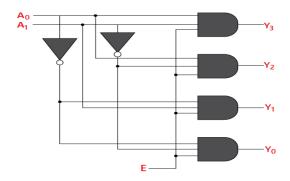

### 2 to 4 line decoder:

In the 2 to 4 line decoder, there is a total of three inputs, i.e.,  $A_0$ , and  $A_1$  and E and four outputs, i.e.,  $Y_0$ ,  $Y_1$ ,  $Y_2$ , and  $Y_3$ . For each combination of inputs, when the enable 'E' is set to 1, one of these four outputs will be 1.

### **Block Diagram:**

#### **Truth Table:**

| Enable | INP            | INPUTS                |                       | OUTPUTS        |                |                |  |

|--------|----------------|-----------------------|-----------------------|----------------|----------------|----------------|--|

| E      | A <sub>1</sub> | <b>A</b> <sub>0</sub> | <b>Y</b> <sub>3</sub> | Y <sub>2</sub> | Υ <sub>1</sub> | Υ <sub>0</sub> |  |

| 0      | Х              | Х                     | 0                     | 0              | 0              | 0              |  |

| 1      | 0              | 0                     | 0                     | 0              | 0              | 1              |  |

| 1      | 0              | 1                     | 0                     | 0              | 1              | 0              |  |

| 1      | 1              | 0                     | 0                     | 1              | 0              | 0              |  |

| 1      | 1              | 1                     | 1                     | 0              | 0              | 0              |  |

The logical expression of the term Y0, Y0, Y2, and Y3 is as follows:

$Y_3=E.A_1.A_0$   $Y_2=E.A_1.A_0'$   $Y_1=E.A_1'.A_0$  $Y_0=E.A_1'.A_0'$

Logical circuit of the above expressions is given below:

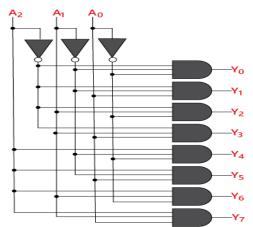

### 3 to 8 line decoder:

The 3 to 8 line decoder is also known as **Binary to Octal Decoder**. In a 3 to 8 line decoder, there is a total of eight outputs, i.e.,  $Y_0$ ,  $Y_1$ ,  $Y_2$ ,  $Y_3$ ,  $Y_4$ ,  $Y_5$ ,  $Y_6$ , and  $Y_7$  and three outputs, i.e.,  $A_0$ ,  $A_1$ , and  $A_2$ . This circuit has an enable input 'E'. Just like 2 to 4 line decoder, when enable 'E' is set to 1, one of these four outputs will be 1.

# **Block Diagram:**

# Truth Table:

| Enable | I              | NPUTS          |    | Outputs               |                       |                       |                       |                       |                |                |    |

|--------|----------------|----------------|----|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|----------------|----------------|----|

| E      | A <sub>2</sub> | A <sub>1</sub> | Ao | <b>Y</b> <sub>7</sub> | <b>Y</b> <sub>6</sub> | <b>Y</b> <sub>5</sub> | <b>Y</b> <sub>4</sub> | <b>Y</b> <sub>3</sub> | Y <sub>2</sub> | Y <sub>1</sub> | Yo |

| 0      | х              | х              | х  | 0                     | 0                     | 0                     | 0                     | 0                     | 0              | 0              | 0  |

| 1      | 0              | 0              | 0  | 0                     | 0                     | 0                     | 0                     | 0                     | 0              | 0              | 1  |

| 1      | 0              | 0              | 1  | 0                     | 0                     | 0                     | 0                     | 0                     | 0              | 1              | 0  |

| 1      | 0              | 1              | 0  | 0                     | 0                     | 0                     | 0                     | 0                     | 1              | 0              | 0  |

| 1      | 0              | 1              | 1  | 0                     | 0                     | 0                     | 0                     | 1                     | 0              | 0              | 0  |

| 1      | 1              | 0              | 0  | 0                     | 0                     | 0                     | 1                     | 0                     | 0              | 0              | 0  |

| 1      | 1              | 0              | 1  | 0                     | 0                     | 1                     | 0                     | 0                     | 0              | 0              | 0  |

| 1      | 1              | 1              | 0  | 0                     | 1                     | 0                     | 0                     | 0                     | 0              | 0              | 0  |

| 1      | 1              | 1              | 1  | 1                     | 0                     | 0                     | 0                     | 0                     | 0              | 0              | 0  |

The logical expression of the term  $Y_0$ ,  $Y_1$ ,  $Y_2$ ,  $Y_3$ ,  $Y_4$ ,  $Y_5$ ,  $Y_6$ , and  $Y_7$  is as follows:

$$Y_0=A_0'.A_1'.A_2'$$

$Y_1=A_0.A_1'.A_2'$

$Y_2=A_0'.A_1.A_2'Y_3=A_0.A_1.A_2'$

$Y_4=A_0'.A_1'.A_2$   $Y_5=A_0.A_1'.A_2$   $Y_6=A_0'.A_1.A_2$  $Y_7=A_0.A_1.A_2$

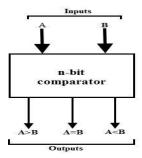

#### **Digital Comparator**

A magnitude digital comparator is a combinational circuit that compares two digital or binary numbers (consider A and B) and determines their relative magnitudes in order to find out whether one number is equal, less than or greater than the other digital number.

Three binary variables are used to indicate the outcome of the comparison as A>B, A<B, or A=B. The below figure shows the block diagram of a n-bit comparator which compares the two numbers of n-bit length and generates their relation between themselves.

### **Types of Magnitude Comparators**

There are different kinds of magnitude comparators which include the following.

## 1- bit Magnitude Comparator

A comparator that compares two binary bits and produces three outputs based on the relative magnitudes of given binary bits is called a 1-bit magnitude comparator.

### Truth Table

The truth table for a 1-bit magnitude comparator is given below.

| Inp | uts |       | <b>Outputs</b> |       |

|-----|-----|-------|----------------|-------|

| Α   | В   | A > B | A = B          | A < B |

| 0   | 0   | 0     | 1              | 0     |

| 0   | 1   | 0     | 0              | 1     |

| 1   | 0   | 1     | 0              | 0     |

| 1   | 1   | 0     | 1              | 0     |

The truth table derives the expressions of A<B, A>B and A=B as below

A<B - A'B A>B - AB' A=B - A'B'+AB

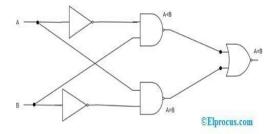

With these expressions, the Circuit diagram can be as follows

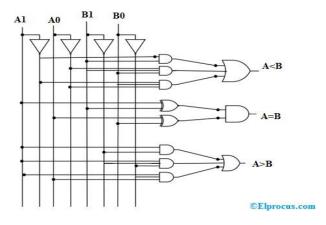

### 2-bit Magnitude Comparator

A comparator that compares two binary numbers (each number having 2 bits) and produces three outputs based on the relative magnitudes of given binary bits is called a 2-bit magnitude comparator.

### **Truth Table**

|                | Inp            | uts            |                |     | Outputs |                   |

|----------------|----------------|----------------|----------------|-----|---------|-------------------|

| $\mathbf{A_1}$ | $\mathbf{A}_0$ | $\mathbf{B}_1$ | $\mathbf{B}_0$ | A>B | A=B     | A <b< th=""></b<> |

| 0              | 0              | 0              | 0              | 0   | 1       | 0                 |

| 0              | 0              | 0              | 1              | 0   | 0       | 1                 |

| 0              | 0              | 1              | 0              | 0   | 0       | 1                 |

| 0              | 0              | 1              | 1              | 0   | 0       | 1                 |

| 0              | 1              | 0              | 0              | 1   | 0       | 0                 |

| 0              | 1              | 0              | 1              | 0   | 1       | 0                 |

| 0              | 1              | 1              | 0              | 0   | 0       | 1                 |

| 0              | 1              | 1              | 1              | 0   | 0       | 1                 |

| 1              | 0              | 0              | 0              | 1   | 0       | 0                 |

| 1              | 0              | 0              | 1              | 1   | 0       | 0                 |

| 1              | 0              | 1              | 0              | 0   | 1       | 0                 |

| 1              | 0              | 1              | 1              | 0   | 0       | 1                 |

| 1              | 1              | 0              | 0              | 1   | 0       | 0                 |

| 1              | 1              | 0              | 1              | 1   | 0       | 0                 |

| 1              | 1              | 1              | 0              | 1   | 0       | 0                 |

| 1              | 1              | 1              | 1              | 0   | 1       | 0                 |

The truth table derives the expressions of A<B, A>B, and A=B as below

$A < B - A_1'B_1' + A_0'B_1B_0 + A_1'A_0'B_0$   $A > B - A_1B_1' + A_0B_1'B_0' + A_1A_0B_0'$  $A = B - (A_0 Ex-Nor B_0) (A_1 Ex-Nor B_1)$

With these expressions, the Circuit diagram can be as follows

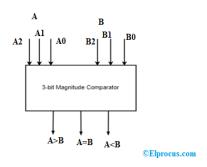

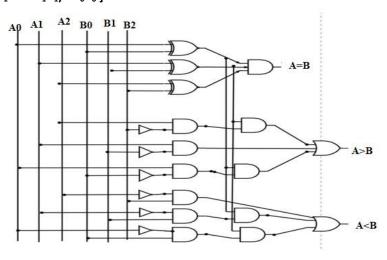

# **3-bit Magnitude Comparator**

A comparator that compares two binary numbers (each number having 3 bits) and produces three outputs based on the relative magnitudes of given binary bits is called a 3-bit magnitude comparator.

The equal functions are  $A_0 = B_0$ ,  $A_1 = B_1$ ,  $A_2 = B_2$ Then A = B=  $(A_0'B_0' + A_0B_0)(A_1'B_1' + A_1B_1)(A_2'B_2' + A_2B_2)$

The output is **A< B** in the cases of

$A_2 < B_2$

$A_2 = B_2$  then  $A_1 < B_1$

$A_2 = B_2$ ,  $A_1 = B_1$  then  $A_0 < B_0$

$A < B = A_2'B_2 + [(A_2'B_2' + A_2B_2) \times A_1'B_1] + [(A_2'B_2' + A_2B_2) \times [(A_1'B' + A_1B_1) \times A_0'B_0]$

The output is A> B in the cases of

A<sub>2</sub>>B<sub>2</sub>

$A_2 = B_2$  then  $A_1 > B_1$

$A_2 = B_2$ ,  $A_1 = B_1$  then  $A_0 > B_0$

$A>B = A_2B_2' + + [(A_2'B_2' + A_2B_2) \times A_1B_1'] + [(A_2'B_2' + A_2B_2) \times A_1'] + [(A_2'B_2' + A_2'B_2) \times A_1'] + [(A_2'B_2' + A_2'B_2) \times A_1'] + [(A_2'B_2' + A_2'B_2' + A_2'B_2') + [(A_2'B_2' + A_2'B_2' + A_2'B_2' + A_2'B_2')] + [(A_2'B_2' + A_2'B_2' + A_2'B_2' + A_2'B_2')] + [(A_2'B_2' + A_2'B_2' + A_2'B_2' + A_2'B_2' + A_2'B_2')] + [(A_2'B_2' + A_2'B_2' + A_2'B_2' + A_2'B_2')] + [(A_2'B_2' + A_2'B_2' + A_2' + A_2'B_2' + A_2' + A_2'B_2' + A_2' + A_2'B_2' + A_2' + A_2'B_2' +$

$[(A_1'B' + A_1B_1) \times A_0B_0']$

#### **MULTIPLEXER**

**Multiplexer** is a combinational circuit that has maximum of 2<sup>n</sup> data inputs, 'n' selection lines and single output line. One of these data inputs will be connected to the output based on the values of selection lines.

Since there are 'n' selection lines, there will be 2<sup>n</sup> possible combinations of zeros and ones. So, each combination will select only one data input. Multiplexer is also called as **Mux**

There are various types of the multiplexer which are as follows:

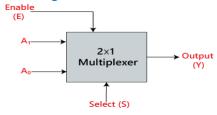

#### 2×1 Multiplexer:

In  $2\times1$  multiplexer, there are only two inputs, i.e.,  $A_0$  and  $A_1$ , 1 selection line, i.e.,  $S_0$  and single outputs, i.e., Y. On the basis of the combination of inputs which are present at the selection line S, one of these 2 inputs will be connected to the output.

#### **Block Diagram:**

#### Truth Table:

| INPUTS         | Output         |

|----------------|----------------|

| S <sub>0</sub> | Y              |

| 0              | A <sub>0</sub> |

| 1              | A <sub>1</sub> |

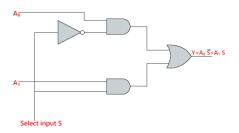

The logical expression of the term Y is as follows:

$Y=S_0'.A_0+S_0.A_1$

Logical circuit of the above expression is given below:

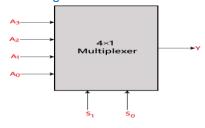

### 4×1 Multiplexer:

In the  $4\times1$  multiplexer, there is a total of four inputs, i.e.,  $A_0$ ,  $A_1$ ,  $A_2$ , and  $A_3$ , 2 selection lines, i.e.,  $S_0$  and  $S_1$  and single output, i.e., Y. On the basis of the combination of inputs that are present at the selection lines  $S^0$  and  $S_1$ , one of these 4 inputs are connected to the output.

#### **Block Diagram:**

### Truth Table:

| INP                   | INPUTS         |                |  |  |  |

|-----------------------|----------------|----------------|--|--|--|

| <b>S</b> <sub>1</sub> | S <sub>0</sub> | Y              |  |  |  |

| 0                     | 0              | A <sub>0</sub> |  |  |  |

| 0                     | 1              | A <sub>1</sub> |  |  |  |

| 1                     | 0              | A <sub>2</sub> |  |  |  |

| 1                     | 1              | A <sub>3</sub> |  |  |  |

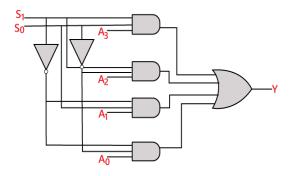

The logical expression of the term Y is as follows:

$$Y=S_1' S_0' A_0+S_1' S_0 A_1+S_1 S_0' A_2+S_1 S_0 A_3$$

Logical circuit of the above expression is given below:

## **DE-MULTIPLEXER**

De-Multiplexer is a combinational circuit that performs the reverse operation of Multiplexer. It has single input, 'n' selection lines and maximum of 2<sup>n</sup> outputs. The input will be connected to one of these outputs based on the values of selection lines.

Since there are 'n' selection lines, there will be 2<sup>n</sup> possible combinations of zeros and ones. So, each combination can select only one output. De-Multiplexer is also called as De-Mux.

There are various types of De-multiplexer which are as follows:

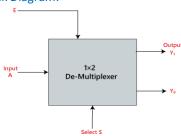

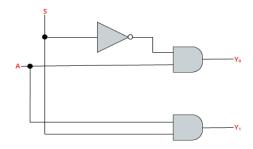

### 1×2 De-multiplexer:

In the 1 to 2 De-multiplexer, there are only two outputs, i.e.,  $Y_0$ , and  $Y_1$ , 1 selection lines, i.e.,  $S_0$ , and single input, i.e., A. On the basis of the selection value, the input will be connected to one of the outputs.

### Block Diagram:

### Truth Table:

| INPUTS         | Out            | put                   |

|----------------|----------------|-----------------------|

| S <sub>0</sub> | Υ <sub>1</sub> | <b>Y</b> <sub>0</sub> |

| 0              | 0              | Α                     |

| 1              | Α              | 0                     |

The logical expression of the term Y is as follows:

$Y_0=S_0'.A$

$Y_1=S_0.A$

Logical circuit of the above expressions is given below:

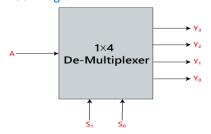

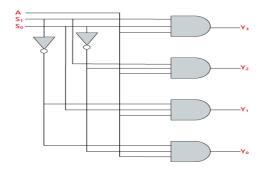

# 1×4 De-multiplexer:

In 1 to 4 De-multiplexer, there are total of four outputs, i.e.,  $Y_0$ ,  $Y_1$ ,  $Y_2$ , and  $Y_3$ , 2 selection lines, i.e.,  $S_0$  and  $S_1$  and single input, i.e., A. On the basis of the combination of inputs which are present at the selection lines  $S_0$  and  $S_1$ , the input be connected to one of the outputs.

# Block Diagram:

### Truth Table:

| INP            | UTS            | Output         |                |                |                |  |  |  |

|----------------|----------------|----------------|----------------|----------------|----------------|--|--|--|

| S <sub>1</sub> | S <sub>0</sub> | Υ <sub>3</sub> | Y <sub>2</sub> | Υ <sub>1</sub> | Y <sub>0</sub> |  |  |  |

| 0              | 0              | 0              | 0              | 0              | А              |  |  |  |

| 0              | 1              | 0              | 0              | Α              | 0              |  |  |  |

| 1              | 0              | 0              | А              | 0              | 0              |  |  |  |

| 1              | 1              | Α              | 0              | 0              | 0              |  |  |  |

The logical expression of the term Y is as follows:

$Y_0 = S_1' S_0' A$

$y_1=S_1' S_0 A$

$$y_2 = S_1 S_0' A$$

$$y_3 = S_1 S_0 A$$

Logical circuit of the above expressions is given below:

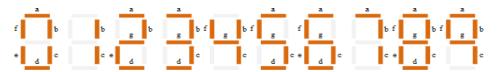

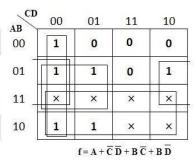

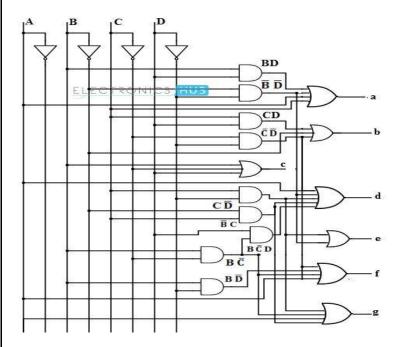

### **SEVEN SEGMENT DECODER**

Seven segment displays are the output display device that provides a way to display information in the form of image or text or decimal numbers.

One of the most commonly used decoder drive is a BCD to 7-segment decoder. In this decoder the outputs are used to drive seven segments.

It is widely used in digital clocks, basic calculators, electronic meters, and other electronic devices that display numerical information.

BCD to seven segment decoder has four input lines A, B, C and D and 7 output lines a, b, c, d, e, f and g. As the numbers which are greater than 9 are not a permitted combination it is assumed that they will not occur.

| Digit | A | В | C | D | а | b | с | d | e | f | g |

|-------|---|---|---|---|---|---|---|---|---|---|---|

| 0     | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 |

| 1     | 0 | 0 | 0 | 1 | 1 | 0 | 0 | 1 | 1 | 1 | 1 |

| 2     | 0 | 0 | 1 | 0 | 0 | 0 | 1 | 0 | 0 | 1 | 0 |

| 3     | 0 | 0 | 1 | 1 | 0 | 0 | 0 | 0 | 1 | 1 | 0 |

| 4     | 0 | 1 | 0 | 0 | 1 | 0 | 0 | 1 | 1 | 0 | 0 |

| 5     | 0 | 1 | 0 | 1 | 0 | 1 | 0 | 0 | 1 | 0 | 0 |

| 6     | 0 | 1 | 1 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 |

| 7     | 0 | 1 | 1 | 1 | 0 | 0 | 0 | 1 | 1 | 1 | 1 |

| 8     | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 9     | 1 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 1 | 0 | 0 |

| 10 | 1 | 0 | 1 | 0 | × | × | × | × | × | × | × |

|----|---|---|---|---|---|---|---|---|---|---|---|

| 11 | 1 | 0 | 1 | 1 | × | × | × | × | × | × | × |

|    | _ |   | _ | _ |   |   |   |   |   |   |   |

| 12 | 1 | 1 | 0 | 0 | × | × | × | × | × | × | × |

|    |   |   |   |   |   |   |   |   |   |   |   |

| 13 | 1 | 1 | 0 | 1 | × | × | × | × | × | × | × |

|    |   |   |   |   |   |   |   |   |   |   |   |

| 14 | 1 | 1 | 1 | 0 | × | × | x | × | × | × | × |

|----|---|---|---|---|---|---|---|---|---|---|---|

| 15 | 1 | 1 | 1 | 1 | × | × | × | × | × | × | × |

From the above truth table, the Boolean expressions of each output functions can be written as

$$a = F_1 (A, B, C, D) = \sum_{i=1}^{n} (0, 2, 3, 5, 7, 8, 9)$$

$$b = F_2(A, B, C, D) = \sum m(0, 1, 2, 3, 4, 7, 8, 9)$$

$$c = F_3 (A, B, C, D) = \sum_{i=1}^{n} (0, 1, 3, 4, 5, 6, 7, 8, 9)$$

$$d = F_4(A, B, C, D) = \sum m (0, 2, 3, 5, 6, 8)$$

$$e = F_5 (A, B, C, D) = \sum m (0, 2, 6, 8)$$

$$f = F_6 (A, B, C, D) = \sum m (0, 4, 5, 6, 8, 9)$$

$$g = F7 (A, B, C, D) = \sum m (2, 3, 4, 5, 6, 8, 9)$$

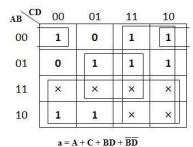

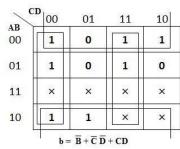

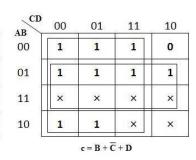

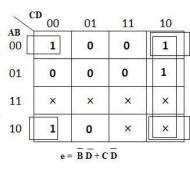

### **K-Map Simplification**

| 00 | 1 | 0 | 1 | 1 |

|----|---|---|---|---|

| )1 | 0 | 1 | 0 | 1 |

| 1  | × | × | × | × |

| 10 | 1 | 1 | × | × |

| BCD | 00 | 01 | 11 | 10 |

|-----|----|----|----|----|

| 00  | 0  | 0  | 1  | 1  |

| 01  | 1  | 1  | 0  | 1  |

| 11  | ×  | ×  | ×  | ×  |

| 10  | 1  | 1  | ×  | ×  |

$g = \overline{B} C + C \overline{D} + B \overline{C} + B \overline{C} + A$

From the above simplification, we get the output values as

$$a = A + C + BD + \overline{B} \overline{D}$$

$$b = \overline{B} + \overline{C} \overline{D} + CD$$

$$c = B + \overline{C} + D$$

$$d = \overline{B} \overline{D} + C \overline{D} + B \overline{C} D + \overline{B} C + A$$

$$e = \overline{B} \overline{D} + C \overline{D}$$

$$f = A + \overline{C} \overline{D} + B \overline{C} + B \overline{D}$$

$$g = A + B \overline{C} + \overline{B} C + C \overline{D}$$

The logic circuit for each output signal of 7- segment display as follow

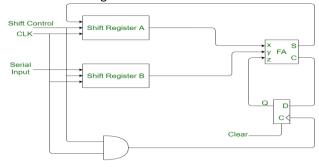

### **SERIAL BINARY ADDER**

Serial binary adder is a <u>combinational logic circuit</u> that performs the addition of two binary numbers in serial form. Serial binary adder performs bit by bit addition. Two shift registers are used to store the binary numbers that are to be added. A single <u>full adder</u> is used to add one pair of bits at a time along with the carry. The carry output from the full adder is applied to a <u>D</u> <u>flip-flop</u>. After that output is used as carry for next significant bits. The sum bit from the output of the full adder can be transferred into a third shift register.

Block Diagram of Serial Binary Adde

### **Shift Registers:**

Shift Register is a group of flip flops used to store multiple bits of data. There are two shift registers used in the serial binary adder. In one shift register augend is stored and in other shift register addend is stored.

#### Full Adder

Full adder is the combinational circuit which takes three inputs and gives two outputs as sum and carry. The circuit adds one pair at a time with the help of it.

## **D Flip-flop**:

The carry output from the full adder is applied on the D flip-flop. Further, the output of D flip-flop is used as a carry input for the next pair of significant bits.

### **Working Process:**

Following is the procedure of addition using serial binary adder:

- Step-1:

- The two shift registers A and B are used to store the numbers to be added.

- Step-2:

- A single full adder is used to add one pair of bits at a time along with the carry.

- Step-3:

The contents of the shift registers shift from left to right and their output starting from a and b are fed into a single full adder along with the output of the carry flip-flop upon application of each clock pulse.

- Step-4:

- The sum output of the full adder is fed to the most significant bit of the sum register.

- Step-5:

- The content of sum register is also shifted to right when clock pulse is applied.

- Step-6:

- After applying four clock pulse the addition of two registers (A & B) contents are stored in sum register.

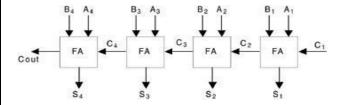

#### **PARALLEL BINARY ADDER**

A digital circuit that is used to perform the addition of two binary numbers & an i/p carry, where the length of one bit is larger than another bit and operates in parallel with equivalent pairs of bits.

The arrangement of parallel adder can be done by arranging the full adders (FAs) in a chain model where the carry o/p from every <u>full adder</u> (FA1) can be linked to the carry i/p of the next full adder (FA2) within the chain.

Two 4-bit binary numbers B  $_4$ B  $_3$ B  $_2$ B  $_1$  and A  $_4$ A  $_3$ A  $_2$ A  $_1$  are to be added with a carry input C  $_1$ . This can be done by cascading four full adder circuits as shown in Figure. The least significant bits A  $_1$ , B  $_1$ , and C  $_1$  are added to the produce sum output S  $_1$  and carry output C  $_2$ . Carry output C  $_2$  is then added to the next significant bits A  $_2$  and B  $_2$  producing sum output S  $_2$  and carry output C  $_3$ . C  $_3$  is then added to A  $_3$  and B  $_3$  and so on. Thus finally producing the four-bit sum output S  $_4$ S  $_3$ S  $_2$ S  $_1$  and final carry output Cout. Such type of four-bit binary adder is commercially available in an IC package.

### **UNIT-3**

### **Unit-3: Sequential logic Circuits**

### Principle of flip-flops operation, its Types

- A flip flop is an electronic circuit with two stable states that can be used to store binary data. The stored data can be changed by applying varying inputs.

- > Flip flop is formed using logic gates such as two NAND and NOR gates which are in turn made of transistors.

- As flip flops have two stable states, hence they are called as Bistablemultivibrators. The two stable states are High (logic 1) and Low (logic 0).

- Flip-flops and latches are fundamental building blocks of digital electronics systems used in computers, communications, and many other types of systems. Flip-flops and latches are used as <u>data storage</u> elements.